Hi team,

Customer have questions.

Could you give answers or comments please?

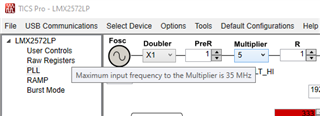

- With regard to datasheet 7.5.2, Do we have to write the R0 register every time I change the N divider, even if FACL_EN in R0 register is set to 1?

- How is VCO calibration used? Do we have to select Assist/No Assist to Partial, Close and Full individually?

- When I use VCO CORE1, which kind of assistance is better?

- Customer found that the larger the N divider, the smaller the spurs. Is the larger the N divider better for noise?

- Is there relationship between MASH ORDER and spurs? (Ex: Larger mash order results in smaller spurs)

- With regard to datasheet 6.5 (5) "clean OSCin signal", Does PNPLL_ 1/f contain OSCin's phase noise?

- With regard to datasheet 6.5 (5), What is N in the PLL_Flat equation?

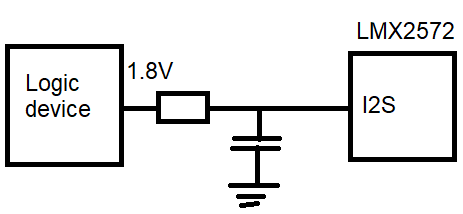

- The higher the OSCin slew rate, the smaller the phase noise.

Is there a relationship between the phase noise of the reference signal and the phase noise of the PLL output?

Kind regards,

Goto

+

+