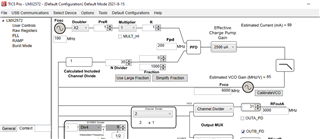

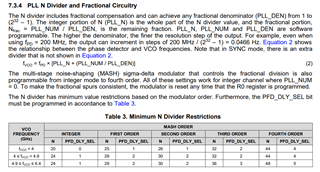

Hi everyone i am using the EVAL board of the LMX2572 but i am unable to understand the formula to calculate the N divider and PLL_NUM/PLL_DEN as well as the calculation behind configuring the register of the given terms. with respective value.

or i can put my question like this :if i want to get a desired frequency from the chip what calculations i have to do and what values will be configured in the register

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.