Hello SIr,

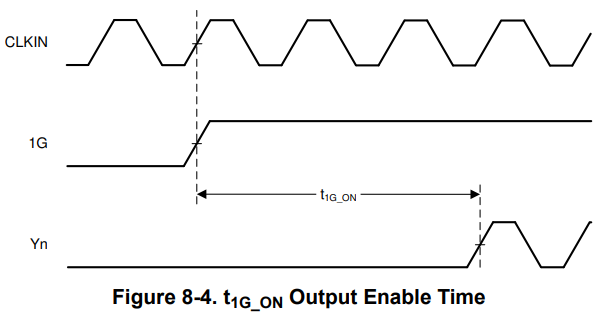

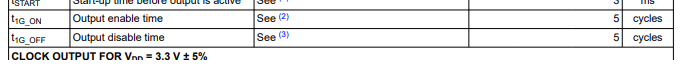

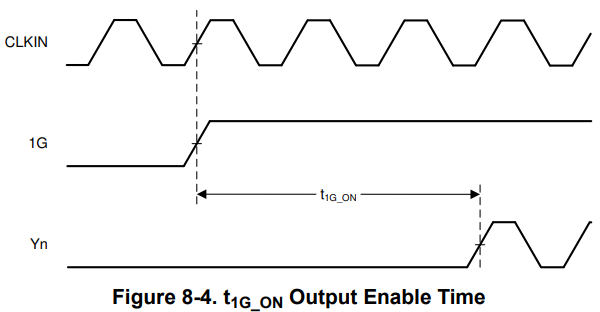

The datasheet of the LMK1C1102PWR mentioned the output needs 5 cycles CLKin,

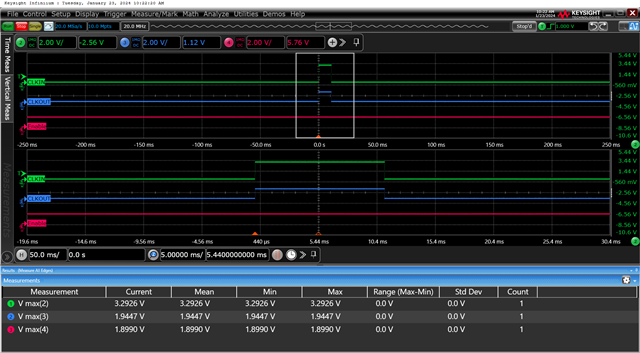

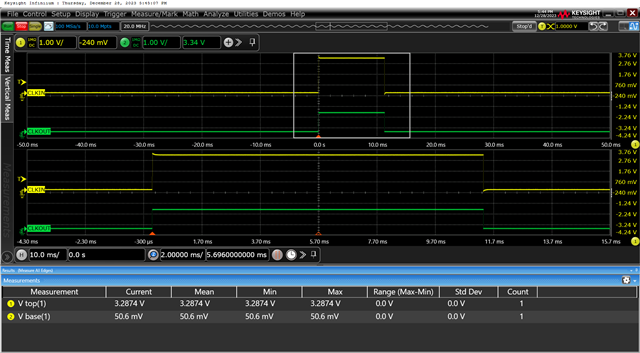

but in our application, the output enabled only used one cycle (as below waveform).

Since currently we're adjusting the FW behavior, we need your opinion to know whether need to adjust it to 5 cycles,

or just keep it at one time. and what's the exact output enable condition of this part, thank you.