Hello,

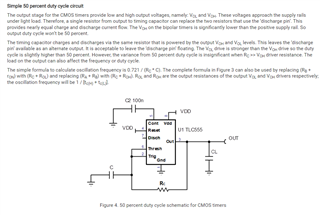

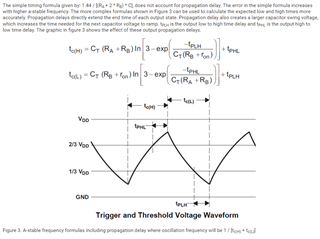

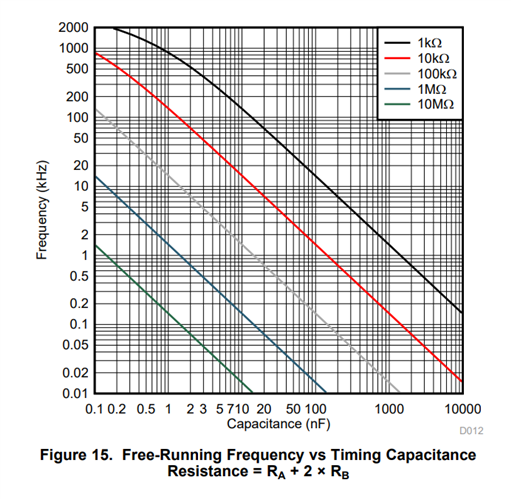

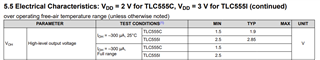

I want to use TLC555 as Astable multivibrator to generate 100KHz square wave with 50% duty cycle. I was using TI calculator in which the propagation delays were included to estimate the output frequency tolerance. I would like to improve the tolerance of output frequency by choosing NPO/C0G capacitor with 5% toleranace but i am not sure how can I calculate the improved toelrance with C0G capacitor since the tool only uses predefined capacitor with 10% tolerance. If i want to use the formulas given in the datasheet there the propagation delays were not included. Could you please let me know how i can calculate/estimate the tolerance of output frequency for 100KHZ square wave with 50% duty cycle operated with Vcc=5V and 3.3V.

Also the tool throws an error when i dont select diode option. It says ''the resistor values are too small, please reduce the capacitor'' can you explain the reason behind this ?

Do you have any alternate cost effective solution for this requirement ?