Other Parts Discussed in Thread: CDCE6214

Hi,

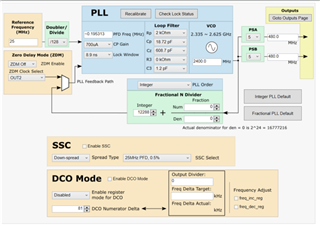

I have a CDCE6214-Q1 dev kit that works very well out of the box with the standard settings. But when I change the default Doubler/Divider (DD) setting from the default 1 and multiply the Integer part of the Fractional N Divider (FND) setting, there are some combinations which unexpectedly prevent the PLL from locking. All settings that I use have the VCO running at 2400MHz. I click Recalibrate and Check Lock Status with all changes.

I need DD = 100 in my application. Please let me know how I may achieve that.

Starting with the default value of DD = 1 and FND = 96 I have lock with VCO = 2400MHz. I can increase both variables up to

DD = 27, FND = 2592, VCO = 2400. (I tried DD = 2, 4, 8, 16, 32 and then down to where it worked)

but

DD = 28, FND = 2688, VCO = 2400 only locks some of the times, and

DD = 29, FND = 2784, VCO = 2400 does not lock

Starting from the opposite side I have lock with

DD = 200, FND = 19200, VCO = 2400

down to

DD = 129, FND = 12384, VCO = 2400

bot no longer at

DD = 128, FND = 12288, VCO = 2400

I have not touched any other settings in the system. Are there loop filter settings etc. that should be changed?

Thanks,

Børge