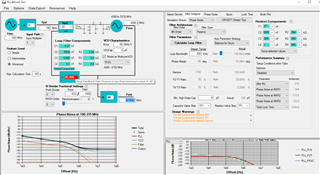

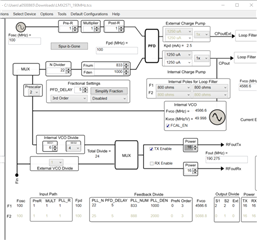

We use the LMX2571 in a design to generate 190 MHz LO for a receiver downconverter.

It loses lock when the board temperature reaches roughly 65 °C. It seems to only loose lock in a narrow temperature range and I’m finding it difficult to repeat the issue reliably (on demand).

I have confirmed that the input clock (a 100 MHz TCXO) and power supply is stable.

Could you please help with suggestions on what to test/measure/verify to narrow down the cause?