Good afternoon,

we are using 4 LMX2594 PLLs in our project and we are facing issues about lock times.

In particular we have the following PLL output frequencies plan [in MHz] to guarantee:

| 3000 |

| 3200 |

| 3400 |

| 3440 |

| 3500 |

| 3800 |

| 3920 |

| 4420 |

| 4480 |

| 4600 |

| 4720 |

| 4740 |

| 4760 |

| 4780 |

| 4800 |

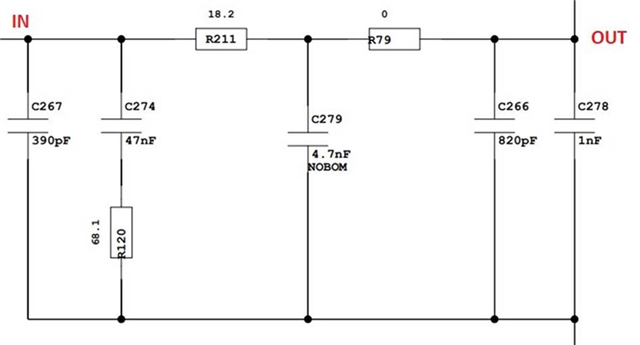

We are using the FULL ASSIST mode and the following loop filter:

The following frequencies changes show lock time in the order of 200us - 400us

- Start Frequency : from 4420 MHz to 4800 MHz -> Stop Frequency: 3920MHz

- Start Frequency: 4600 -> Stop Frequency: 3000 MHz, 3400 MHz

- Start Frequency: 4480 MHz -> Stop Frequency: 3000 MHz, 3200 MHz, 3400 MHz

- Start Frequency: 4420 MHz -> Stop Frequency: 3000 MHz, 3200 MHz, 3400 MHz

- Start Frequency: 4600 MHz -> Stop Frequency: 3440 MHz

- Start Frequency: 4480 -> Stop Frequency: 4420 MHz, 3440 MHz

Even using the loop filter coming from PLLatinum tool does not reduce lock times.

We are measuring the lock time enabling a counter after the last PLL SPI writing and freezing it when MUXout pin (set as lock detect) goes to logic 1.

What we should check in order to improve the lock times?

Thanks for the support