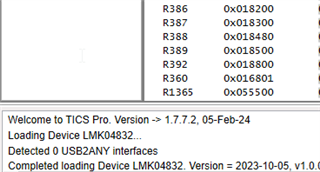

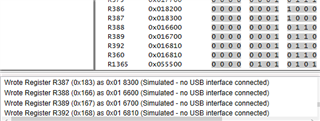

The TICS Pro (V1.7.7.2) Register Map has inconsistency. see below - the last few entries

R387 0x018300

R388 0x016600 -- the left and right side address mismatch

R389 0x016700 -- the left and right side address mismatch

R392 0x016810 -- the left and right side address mismatch

R360 0x016810

R1365 0x055500