Part Number: LMK04832

Could someone please unlock the following thread:

I finally have the time to tackle it...

Best regards,

Brad

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: LMK04832

Could someone please unlock the following thread:

I finally have the time to tackle it...

Best regards,

Brad

Hello Brad,

I'm unsure how to unlock a thread, in the meantime while I figure it out, I have copied Derek's response below:

"The charge pump on LMK04832 PLL1 is maximum 3.3V, so if you need to pull at the top of the range you're going to have issues. You may need to use an active op-amp circuit to gain up the charge pump signal by a factor of 5/3.3 to access the full pull range.

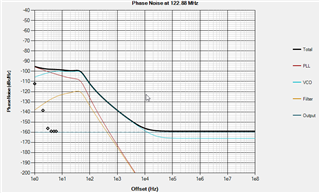

The pull range (or more precisely, the VCO gain) will definitely have an impact on the loop stability as well. The default PLL1 loop filter, for example, is designed for a 2.5kHz/V gain slope, resulting in the following 40Hz, 41° phase margin loop filter:

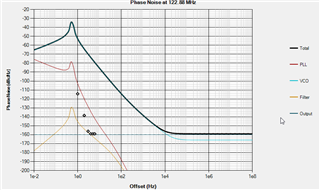

Just to demonstrate the issue, I now set the gain 1000x lower, to 2.5Hz/V. I change nothing else. My new loop bandwidth is 0.5Hz and my phase margin is 4.5°.

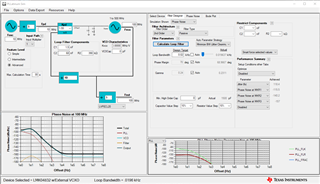

You must design your loop filter with the VCO gain in mind. PLLatinum Sim can help with this, offering a way to set the Kvco gain characteristic for your oscillator.

Let me know if you have any other questions in the meantime.

Best,

Andrea

Quick sidebar question:

If my VCXO only has +/- 4Hz pullability, am I constrained to 8 Hz loop bandwidth?

Not necessarily. Even if you can only change by ±4Hz, you may still be able to jump from +4Hz to -4Hz much faster than 8Hz loop bandwidth.

The tuning range of the VCXO sets Kvco in PLLatinum Sim, and while loop bandwidth is impacted by Kvco, it is also impacted by Kpd, Fpd, and loop filter coefficient values. If you have a high enough Fpd and Kpd value, and you select loop filter coefficients that do not significantly limit the bandwidth, higher bandwidths are possible. As an example, I tested a 10MHz reference and 100MHz VCXO with 2Hz/V tuning range in PLLatinum Sim, and I can see that at maximum gain and certain loop filter values I can get 20Hz loop bandwidth.

However, you might run into an effect that is NOT modeled by PLLatinum Sim: the modulation bandwidth of the VCXO. Even if you can change the voltage at the tuning port very quickly, in practice a narrowband VCOCXO can't respond as quickly to tuning port modulation. The Crystek CVHD-950 VCXO on the LMK04832EVM has >10kHz modulation bandwidth; sampling some VCOCXOs on various distributors, I see values of 1kHz or less very commonly, some pushing down to 100Hz or lower. The rolloff from the modulation bandwidth will add another pole to the system, which can impact stability and loop bandwidth if the pole is too close to the other poles set by the PLL and loop filter characteristics. Try to keep the loop bandwidth at least a factor of 10 smaller than the VCXO modulation bandwidth if possible.