Hello team,

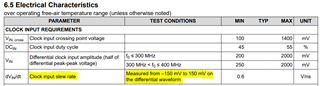

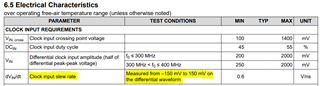

On the datasheet, the input clock slew rate is minimum 0.6V/ns when differential clock. Would it be same for single ended clock, if the amplitude is 300mVpp?

Best Regards,

Kei Kuwahara

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello team,

On the datasheet, the input clock slew rate is minimum 0.6V/ns when differential clock. Would it be same for single ended clock, if the amplitude is 300mVpp?

Best Regards,

Kei Kuwahara

Hello Kei,

The input slew rate needs to be 0.5x what's shown for the differential input slew rate requirement. So it needs to be 0.3V/ns. This is because for a differential signal you subtract the swig of each pin (pos - neg), which results in double the swing. Let me know if you need anything else.

Good luck,

Andrea