Other Parts Discussed in Thread: LMK04828,

-

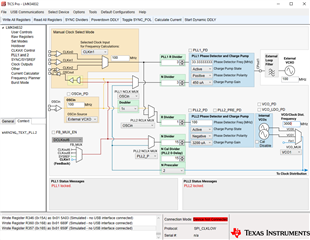

The customer mentioned the option for inputting External Clock, hence we are thinking of feeding external clock input to CLKIN1 of LMK04832

-

The External Input clock will be 100MHz with good phase noise of -150dBc/Hz

-

On-board reference clock input to CLKIN0, which is also a 100MHz OCXO part: KLNBNTE100MFNFCAB

-

OSCIn Input will also be 100MHz VCXO

-

Is it okay to feed the PLL1 Reference clock of 100MHz

-

Is the PFD of PLL1 will have any issues? Due to high R & N-divider

-

What value of PFD, Do you suggest for this case? As Fpd1 is 40MHz for PLL1