Hello:

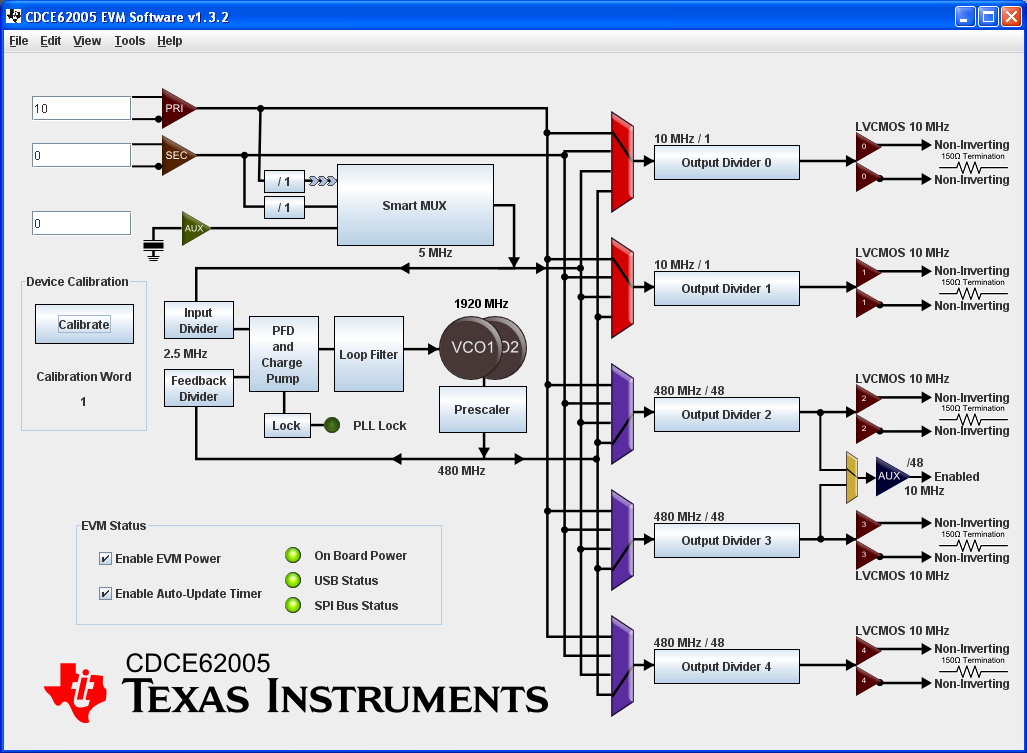

I am working with the CDCE62005EVM module and I cannot get the device to PLL lock. I have a single ended 10MHz CMOS input on PRI_N and would like a 10MHz output.

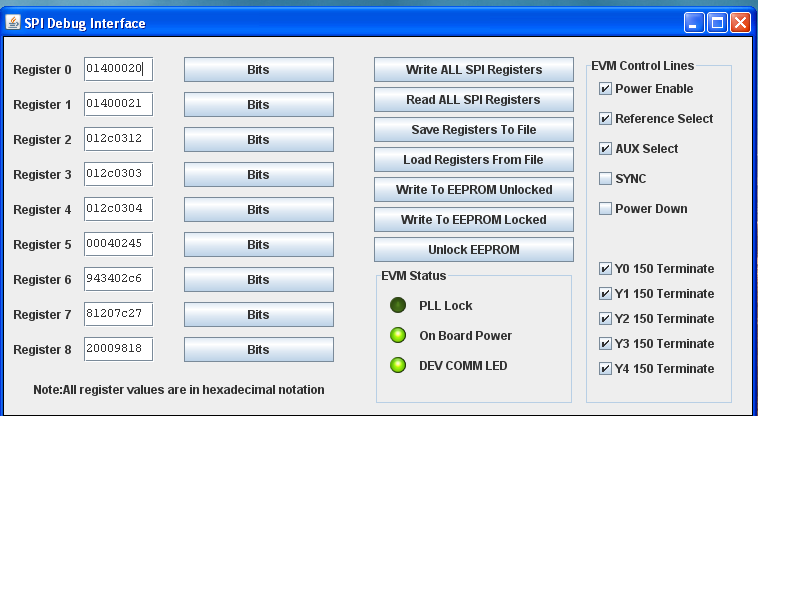

Attached are two files: 1) register configuration and 2) GUI settings.

Any help is greatly appreciated!

Kerri