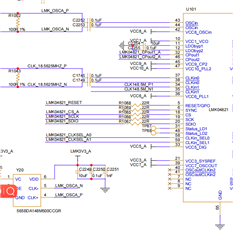

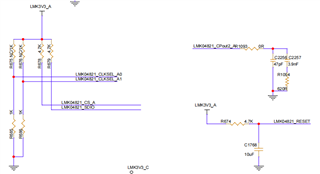

The chip is powered normally at 3.3V.SPI communication fail. There are only resistors between the FPGA and LMK04821, without any other components.

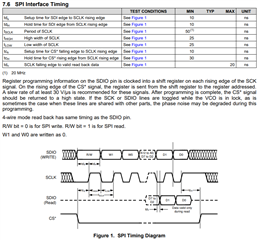

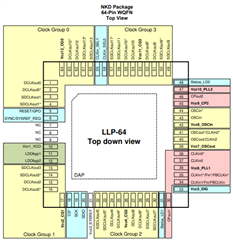

The LMK04821 is controlled by the FPGA, CSn cannot be pulled high. Changing the terminating resistor on CSn to 1K and reducing the distance to the LMK04821 to 1cm did not resolve the issue. FPGA and LMK04821 share the common ground.Measurements show:

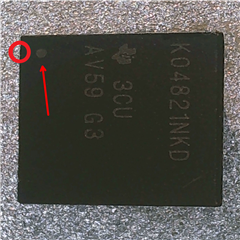

1. Upon system power-up without FPGA loading,the pin state of the FPGA is weak pull-up.Measuring the voltage across the resistor, the voltage on the LMK04821 side is 1.56V, and on the FPGA side is 2.10V, so the input current of the CSn pin is 540uA.

2.While the FPGA is loaded and the SPI interface remains in its default state without sending data, driving CSn pin to a high level leads to the voltage on the LMK04821 side is 1.62V and the FPGA side is 3.30V, the input current of the CSn pin is 1.68mA.

3. Under the second testing condition, multiple attempts were made to reset the LMK04821 chip via the Reset pin, while monitoring the CSn signal line on the LMK04821 side. However, nothing changed. According to the datasheet regarding the CSn pin current, CSn can only be an input interface, with a maximum current of ±5uA. However, the actual measurement differs from the datasheet by several hundred times, indicating an abnormal power state for CSn.

Given that LMK04821 only needs stable 3.3V power and consistent high or low levels on the reset pin for proper operation, Is there any possibility that the above error state may occur, what is the best way to rectify the problem?

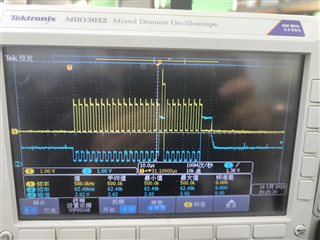

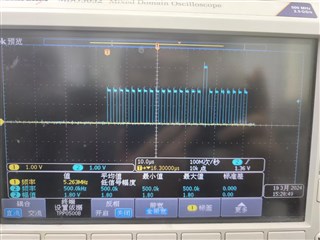

plus,in normal operation(terminating resistor 22ohm,SDIO pull-up 4.7K to 3.3V),sck high voltage is only 2V.SDIO cannot be held low.