Other Parts Discussed in Thread: LMK04832

Now we are developing a navigation payload.

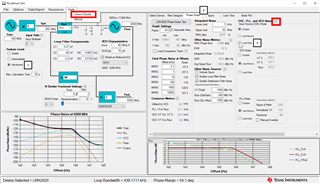

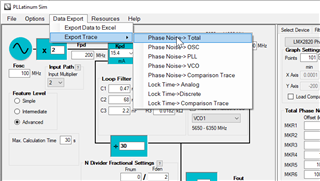

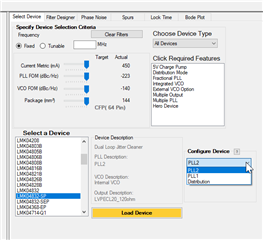

When we receive a 10.23MHz clock with a jitter of +/- 2nsec, we'd like to clean the clock using a dual PLL scheme.

We use an output clock of 122.76MHz (12 times 10.23MHz).

Could you suggest how much the 10.23MHz clock can be cleaned from +/- 2ns?

Best regards

Jae-Heung Yeom