Other Parts Discussed in Thread: LMK04610, LMK04832

Hi,

I am working on a project using the Xilinx (AMD) ZCU216 development kit with the CLK104 add-on card. The CLK104 board uses the LMK04828.

I am providing a 10MHz reference signal to the LMK chip using the J11 SMA connector on the CLK104 board connected to the CLKin0 input of the LMK. This same 10MHz reference will be provided to another development kit as well. The objective is to generate a 10MHz output clock form the LMK04828 across multiple boards that will be frequency and phase locked to each other. This 10MHz output will be sent to the FPGA to drive logic that will need to be synchronized across multiple boards.

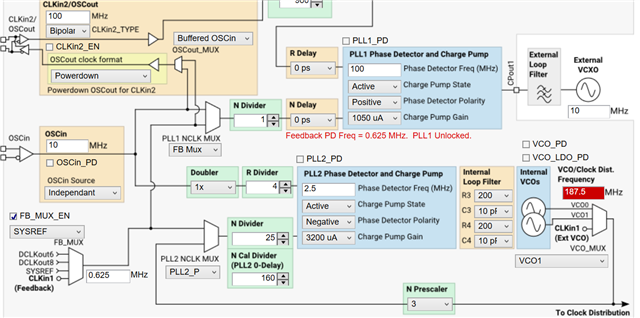

The diagram below shows how I think I need to configure the LMK chip. Also included is the corresponding register dump file from TICS. For now, I am using the SDCLKout11 output, which is connected to an SMA connector on the CLK104 board for easy monitoring.

R0 (INIT) 0x000090 R0 0x000010 R2 0x000200 R3 0x000306 R4 0x0004D0 R5 0x00055B R6 0x000600 R12 0x000C51 R13 0x000D04 R256 0x01006C R257 0x010155 R258 0x010255 R259 0x010301 R260 0x010422 R261 0x010500 R262 0x010673 R263 0x010703 R264 0x01086C R265 0x010955 R266 0x010A55 R267 0x010B00 R268 0x010C22 R269 0x010D00 R270 0x010EF0 R271 0x010F30 R272 0x01106C R273 0x011155 R274 0x011255 R275 0x011301 R276 0x011422 R277 0x011500 R278 0x011673 R279 0x011703 R280 0x01186C R281 0x011955 R282 0x011A55 R283 0x011B01 R284 0x011C22 R285 0x011D00 R286 0x011E72 R287 0x011F03 R288 0x012078 R289 0x012155 R290 0x012255 R291 0x012301 R292 0x012422 R293 0x012500 R294 0x012670 R295 0x012733 R296 0x01286C R297 0x012955 R298 0x012A55 R299 0x012B00 R300 0x012C22 R301 0x012D00 R302 0x012EF0 R303 0x012F30 R304 0x01306C R305 0x013155 R306 0x013255 R307 0x013301 R308 0x013422 R309 0x013500 R310 0x013673 R311 0x013703 R312 0x013820 R313 0x013903 R314 0x013A01 R315 0x013B2C R316 0x013C00 R317 0x013D01 R318 0x013E03 R319 0x013F0D R320 0x014009 R321 0x014100 R322 0x014200 R323 0x014331 R324 0x0144FF R325 0x01457F R326 0x014618 R327 0x01470A R328 0x014806 R329 0x014946 R330 0x014A06 R331 0x014B06 R332 0x014C00 R333 0x014D00 R334 0x014EC0 R335 0x014F7F R336 0x015013 R337 0x015102 R338 0x015200 R339 0x015300 R340 0x015401 R341 0x015500 R342 0x01567D R343 0x015703 R344 0x0158C0 R345 0x015900 R346 0x015A01 R347 0x015BDA R348 0x015C20 R349 0x015D00 R350 0x015E00 R351 0x015F3E R352 0x016000 R353 0x016104 R354 0x016264 R355 0x016300 R356 0x016400 R357 0x0165A0 R369 0x0171AA R370 0x017202 R380 0x017C15 R381 0x017D33 R358 0x016600 R359 0x016700 R360 0x016819 R361 0x016959 R362 0x016A20 R363 0x016B00 R364 0x016C00 R365 0x016D00 R366 0x016E1B R371 0x017300 R386 0x018200 R387 0x018300 R388 0x018400 R389 0x018500 R392 0x018800 R393 0x018900 R394 0x018A00 R395 0x018B00 R8189 0x1FFD00 R8190 0x1FFE00 R8191 0x1FFF53

I want to confirm that my understanding of the configuration is accurate and that I can expect the behaviour to be as I described:

- With this configuration, should I expect the CLKin0 input and the SDCLKout11 output to be both frequency and phase aligned?

- If I configure LMK chips similarly on different boards and provide them an equivalent 10MHz reference can I expect the SDCLKout11 outputs on all boards to be aligned?

- Do I need to somehow trigger a SYNC event in order to get phase alignment to occur? I saw mention of this in a different post.

I can provide additional info if needed. Please let me know if anything isn't clear.