Hi,

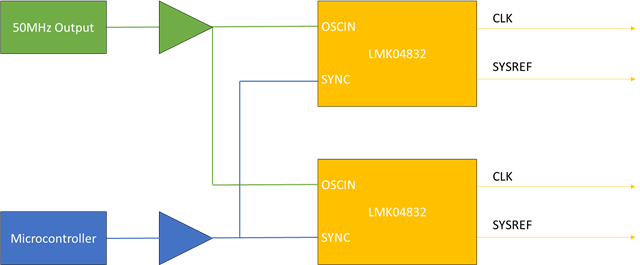

Could you please sanity check my intended implementation to produce frequency-aligned and phase-aligned clock and SYSREF outputs from multiple LMK04832s? Based on some research, I believe this should result in something at least frequency aligned, but am unsure as to the accuracy of the phase-alignment:

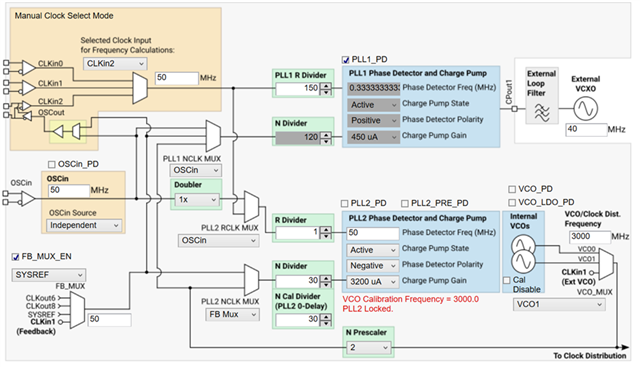

- All LMK04832s are operating in PLL2 Single Loop Mode with an external loop filter

- All LMK04832s operate in cascaded 0-delay mode and the feedback MUX is set to the internal SYSREF generated by the VCO

- All LMK04832s receive a phase-matched 50MHz clock input to OSCIN, which feeds PLL2

- All LMK04832s receive a phase-matched SYNC input signal that triggers a number of SYSREF pulses

In 0-delay mode, is the phase relationship from input clock to output clock deterministic between LMK04832s? Will the outputs from both LMK04832s be perfectly phase-aligned or is there some tolerance?

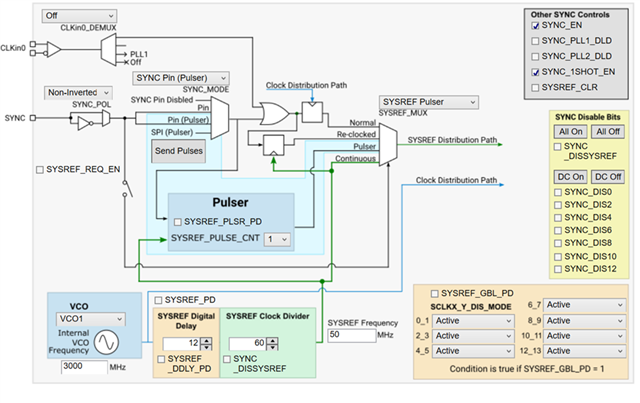

Some block diagrams and images from TICS as a visual:

Thanks,

Matthew