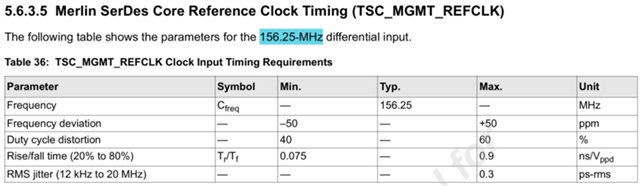

Part Number: LMK05318B

Other Parts Discussed in Thread: LMK05318

Hi Team,

Could you pls suggestion does it support 312.5MHz / 25ppm? Thanks.

Regards,

Hailiang

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Hailiang,

Are you asking if the 312.5MHz outputs can be pulled +/- 25 ppm?

The answer is yes. The LMK05318B BAW VCO (on APLL1) can be pulled +/- 100ppm.

Regards,

Jennifer

Hi Jennifer,

If the output is set to 312.5MHZ + 25ppm, will it affect jitter?

Regards,

Hailiang

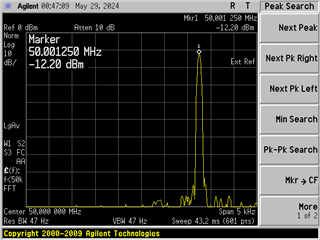

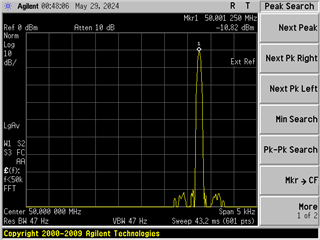

Hi Hailiang,

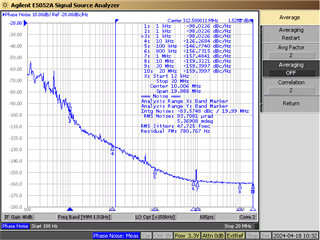

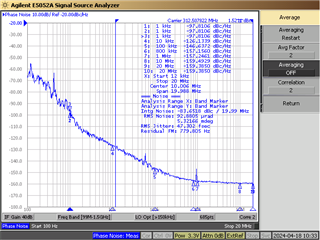

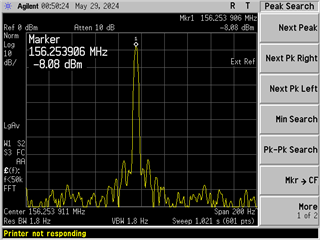

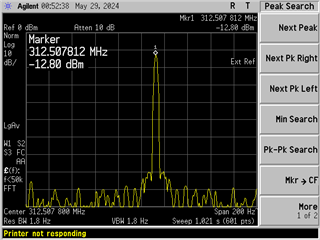

The jitter is still within spec. Please see example plots comparing between 0 and + 25ppm offset on 312.5MHz outputs. Note that the DPLL is locked in both of these pictures. The XO input is sourced from a signal generator (SMB100A).

0ppm:

25ppm:

Regards,

Jennifer

Hi Jennifer,

Thanks for your support.

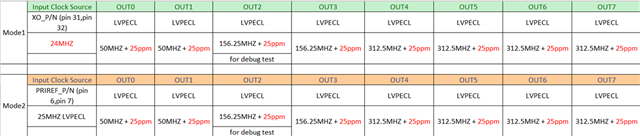

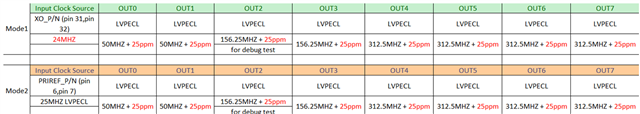

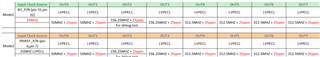

Please help provide the LMK05318BRGZR profile for 312.5MHZ + 25ppm according to the table below.

|

Mode1 |

Input Clock Source |

OUT0 |

OUT1 |

OUT2 |

OUT3 |

OUT4 |

OUT5 |

OUT6 |

OUT7 |

|

XO_P/N (pin 31,pin 32) |

LVPECL |

LVPECL |

LVPECL |

LVPECL |

LVPECL |

LVPECL |

LVPECL |

LVPECL |

|

|

24MHZ |

50MHZ |

50MHZ |

156.25MHZ |

156.25MHZ |

312.5MHZ + 25ppm |

312.5MHZ + 25ppm |

312.5MHZ + 25ppm |

312.5MHZ + 25ppm |

|

|

|

for debug test |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

Mode2 |

Input Clock Source |

OUT0 |

OUT1 |

OUT2 |

OUT3 |

OUT4 |

OUT5 |

OUT6 |

OUT7 |

|

PRIREF_P/N (pin 6,pin 7) |

LVPECL |

LVPECL |

LVPECL |

LVPECL |

LVPECL |

LVPECL |

LVPECL |

LVPECL |

|

|

25MHZ LVPECL |

50MHZ |

50MHZ |

156.25MHZ |

156.25MHZ |

312.5MHZ + 25ppm |

312.5MHZ + 25ppm |

312.5MHZ + 25ppm |

312.5MHZ + 25ppm |

|

|

|

for debug test |

Regards,

Hailiang

Hi Hailiang,

What is the jitter spec for the 50MHz and 156.25MHz outputs?

The LMK05318B does not support individual ppm offset setting. This means that if VCO1 is set to 2500MHz +25ppm, then all outputs from APLL1/VCO1 will also have the +25ppm offset.

If you want to output both 50MHz/156.25MHz and the 312.5MHz+25ppm, then the 50MHz/156.25MHz outputs will have to come from APLL2/VCO2.

Regards,

Jennifer

Hi Jennifer,

Noted. Please set 50MHz and 156.25MHz + 25ppm too.

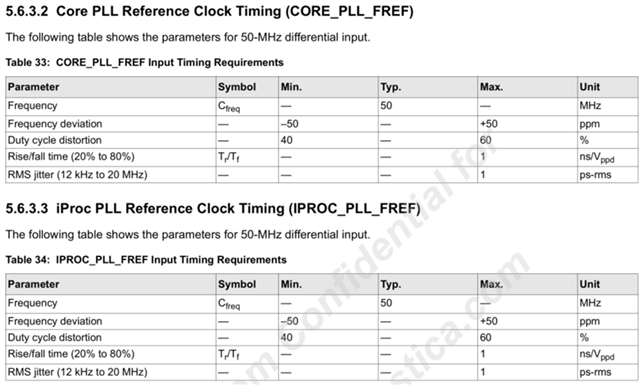

Bellow is the jitter spec for the 50MHz and 156.25MHz outputs

Regards,

Hailiang

Hi Hailiang,

Since 50MHz and 156.25MHz are also +25ppm, all output clocks are from the same BAW VCO 2500MHz. I'll collect the phase noise and share with you.

-Riley

Hi Hailang,

Here is phase noise of output clocks. All clocks have jitter meet this spec.

Model 1: Free-run with XO 24MHz:

50MHz + 25ppm:

156.25MHz + 25ppm:

312.5MHz + 25ppm:

Model 2: DPLL lock with 25MHz input:

50MHz + 25ppm:

156.25MHz + 25ppm:

312.5MHz + 25ppm:

-Riley

Hi Riley, Jennifer,

Thanks for your support. Could you please help provide the LMK05318BRGZR firmware for all output +25ppm?

Regards,

Hailiang

Hailiang,

This config 24MHz XO, 25MHz input.tcs is set for 0ppm.

For +25ppm testing, you could simply adjust reference source by +25ppm and see the update on output.

Mode 1 (free-run): adjust XO source

Mode 2 (DPLL): adjust input reference source

-Riley

Hi Riley,

Thanks. But customer want to keep the reference source by 0ppm and configure the LMK05318B to output +25ppm.

So could you provide the FW that makes the output +25 ppm?

Regards,

Hailiang

Hi Riley,

May I have your reply by your today since there is a long delay? Thanks.

Regards,

Hailiang

Hi Hailiang,

This config uses 24MHz XO and 25MHz input. PLL1 is tuned with +25ppm so all outputs are +25ppm.

24MHz XO, 25MHz input, OUTx + 25ppm.tcs

-Riley

Hi Riley,

Using .tcs file you shared to test, we found OUT3 is 50MHz, OUT4 and OUT5 are 156MHz, which does not match the customer requirements. Attach again.

Please help to check the config and update.

Regards,

Hailiang

Hi Hailaing,

Did you do "write all regs" and "soft-reset chip" after loading the config?

-Riley

Hi Riley,

The customer did the following steps: load config -> program EEPROM -> power cycle. Customer tried "write all registers" and "soft reset chip" after loading the config, the output was also incorrect.

Regards,

Hailiang

Hi Hailiang,

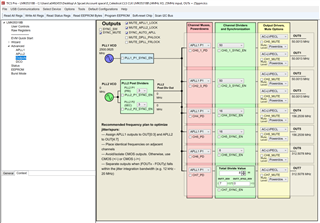

I don't have problem with Riley's configuration.

Power up --> Load the configuration file

Hi Noel, Riley,

The output seems does not match the customer requirement.

GUI:

Customer requirement:

I update the configuration by changing the channel dividers. But pls confirm will this affect output performance?

Regards,

Hailiang