PLC_LMK_V3 WIP.tcsPLC_LMK_V_0_0_2.tcs

Fitted LMK power modification and re-tested board. LMK clock issue still exists.

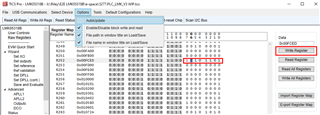

Used TICSPro v1.7.7.2 to capture state of LMK05318B. Added 4 captures to this ticket from board S/N 037 in the process of powering up as follows:

-

LMK powered up with no PRIREF or SECREF. 10MHz out is OK.

-

PRIREF applied. LMK exited holdover. 10MHz out went to wrong frequency

-

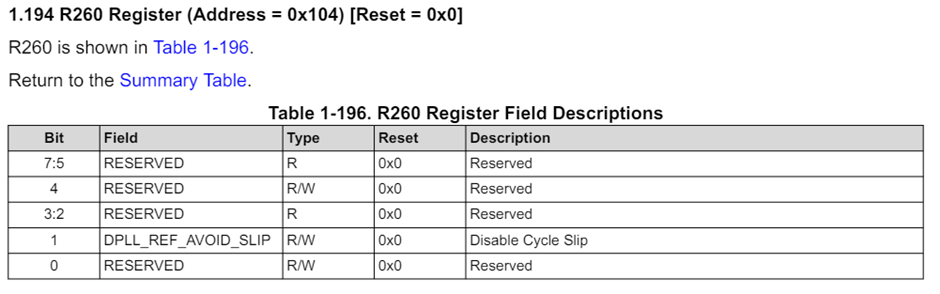

R14, R20, R123, R167 & R411 changed value

-

-

PRIREF removed. LMK back into holdover. 10MHz out recovered

-

R14, R123, R167 & R411 changed value

-

-

PRIREF reapplied. LMK locked. 10MHz out is good

-

R14, R167 & R411 changed value

-

I’ve just added a video showing the 10MHz out for steps 1 & 2 above.

Note: R161 & R162 were dynamically changing all the time.

Note: The original programming file was generated under the older TICSPro V1.7.5.7, and the release notes indicate there have been many improvements made to the LMK05318B profile since then.3. PRIREF removed. LMK in good state. R161 and R162 dynamically changing.tcs4. PRIREF reapplied. LMK in good state. R161 and R162 dynamically changing.tcs1. PRIREF absent. LMK just powered on. LMK in good state. R161 and R162 dynamically changing.tcs2. PRIREF applied. LMK in bad state. R161 and R162 dynamically changing.tcs