Hi team,

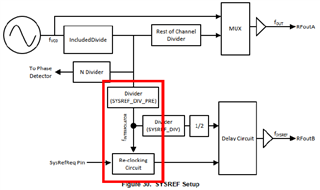

1. My customer plan to output the clock from SysRefReq pin to RFoutB. In SYSREF Setup in the figure below, How much is the jitter in Re-clocking circuit?

2. My customer thinks Divider's clock will be reclocked, how many times behind the above frequency?

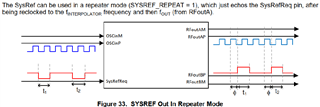

3. My customer plans to configure SYSREF Out In Repeater Mode of LMX2594.which signal should be synchronized with the signal which inputs to SysRefReq, OSCin?RFoutA?

4. Regarding the delay Φ on RFoutA, Is this delay Φ always same value? or does the delay Φ have the jitter?

Best regards,

Shunsuke Yamamoto