Hi,

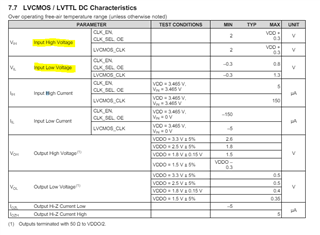

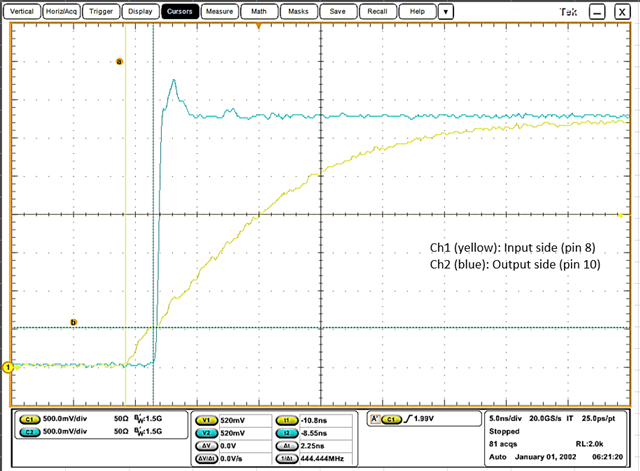

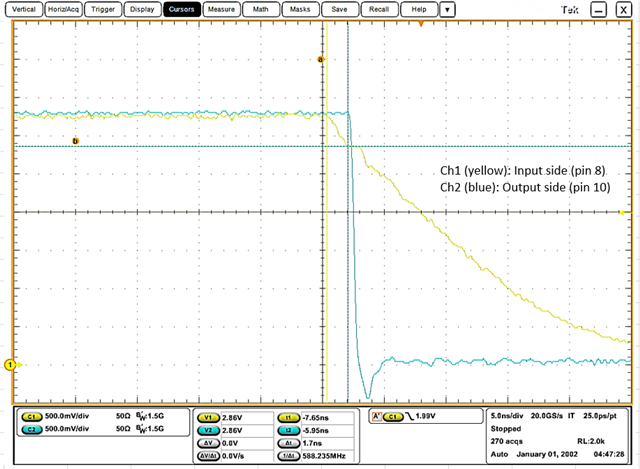

It appears that VIL and VIH of the LVCMOS_CLK pin do not satisfy the characteristics. Without considering the transmission delay of Tpd = 1 to 2.2 ns, the output of all 4 channels seemed to change at approximately 0.45 V and approximately 2.9 V.

We have verified this using official TI samples and commercially purchased products, and the results are similar and there appears to be no lot dependence.

Is it possible to get any comments?

Thanks,

Conor