Other Parts Discussed in Thread: TLC555

Tool/software:

Hello,

Currently, in the process of using TLC555QDRQ1, we need to confirm some technical related issues, as described below:

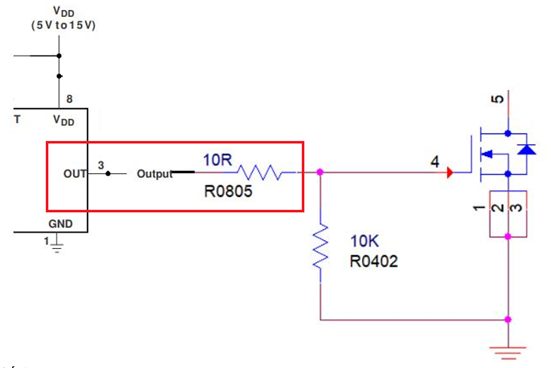

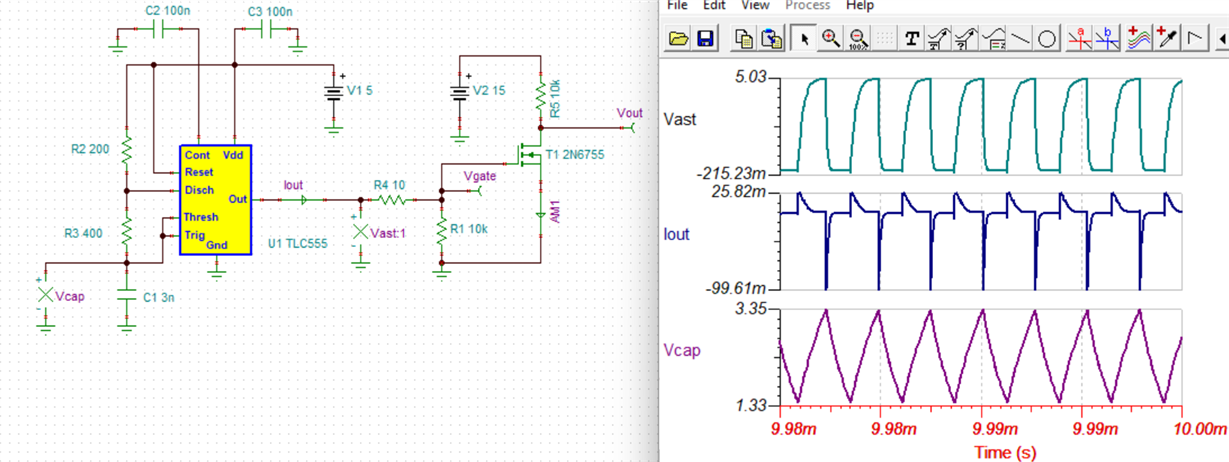

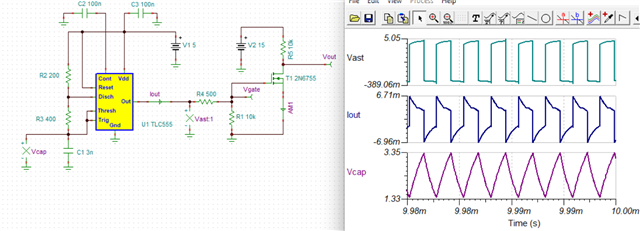

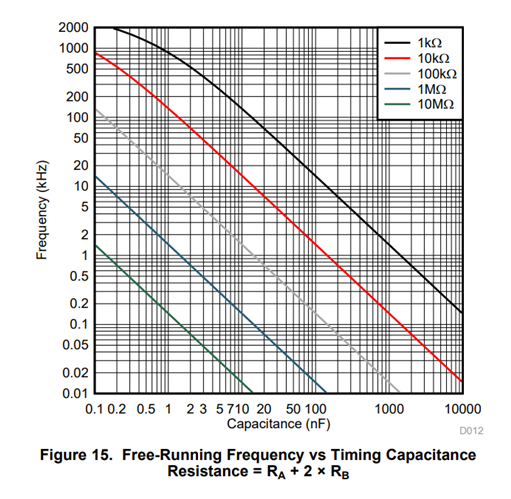

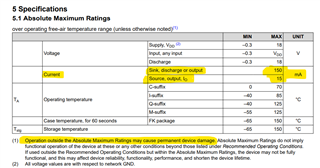

Question 1: We use TLC555-Q1 to drive MOS (MOSFET, N-CH, 2.9A, 100V, DMN10H170SFGQ-7). Connect a 10Ω to MOS at the OUT pin of TLC555QDRQ1, and the frequency is about 500Khz. During the fast switching process of MOS, the TLC555QDRQ1 driving power supply 15V is loaded on 10Ω. Will the generated inrush current affect the OUT pin of TLC555QDRQ1?

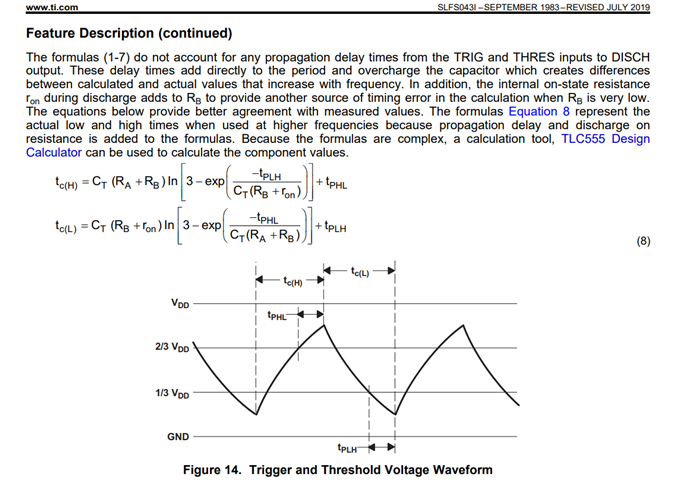

Question 2: If the internal resistance of TLC555QDRQ1 is taken into account, will the inrush current affect the OUT pin of 555?

Question 3: If long-term use or aging life is considered, will the inrush current in this scenario affect the OUT pin of TLC555QDRQ1 multiple times?