Tool/software:

Hello,Team,

I have questions about CDCE913PW.

Are there any issue that output clk freqency is not lock such as freqency is keeping shift?

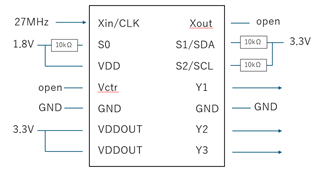

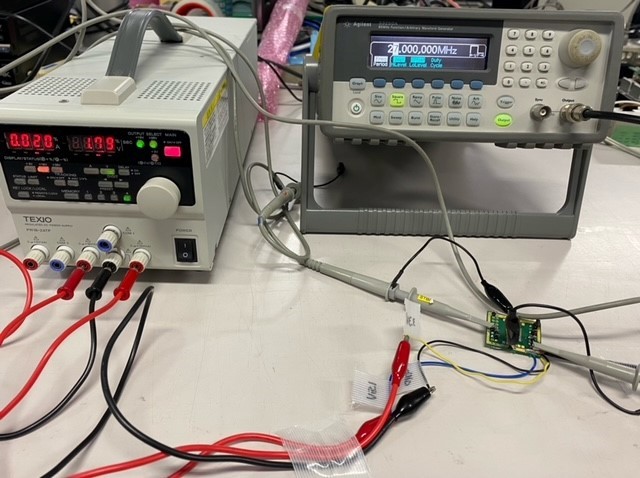

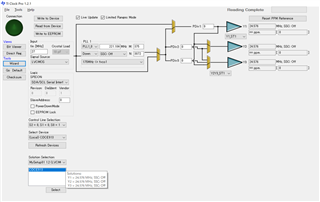

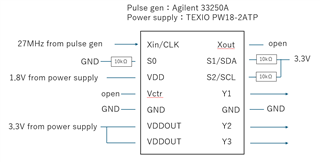

We use this device with below register setting.

<register setting>

0x00:81 /0x01:09 /0x02:B4 /0x03:09 /0x04:03 /0x05:50 /0x06:40 /0x07:0 /0x08:0 /0x09:0

0x0A:0 /0x0B:0 /0x0C:0 /0x0D:0 /0x0E:0 /0x0F:0 /0x10:0 /0x11:0 /0x12:0 /0x13:0 /0x14:0D

0x15:01 /0x16:0 /0x17:0 /0x18:C0 /0x19:04 /0x1A:82 /0x1B:07 /0x1C:C0 /0x1D:04 /0x1E:82 /0x1F:07

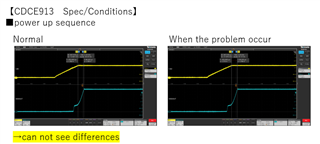

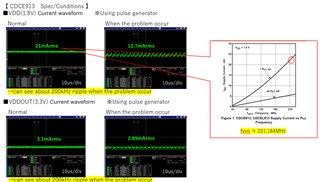

In rare cases, if you turn the power off and on again, Output frequency keeps shifting that is not desired.(but Y1Y2Y3 out put are in sync.)

As you can see with above register setting ,We use Y1Y2Y3 output are the same frequency from the same div.

In the first place, Does the clock output even though the output is not stable when the power is turned on?

Normally, a stable clock is output after a while, but in rare cases(above case) it continues to be output without being stable.

We guess something wrong with PLL.

Thank you for your support