Tool/software:

Hi Team,

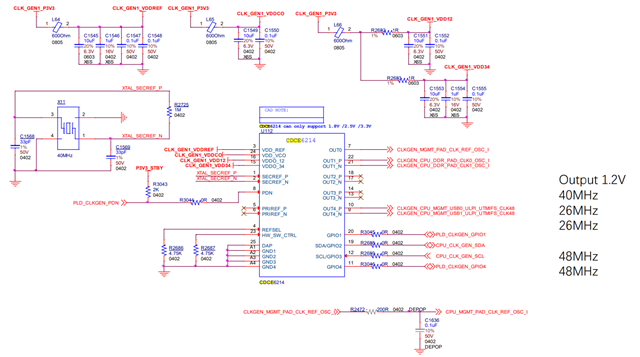

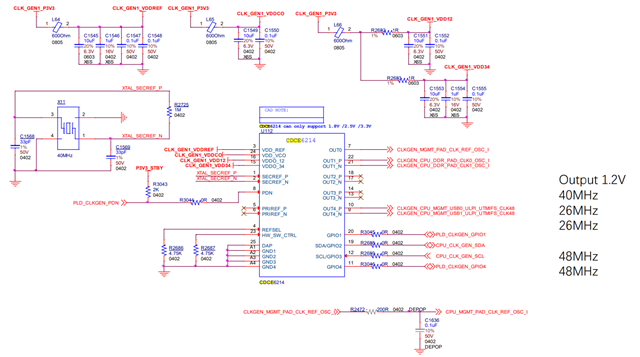

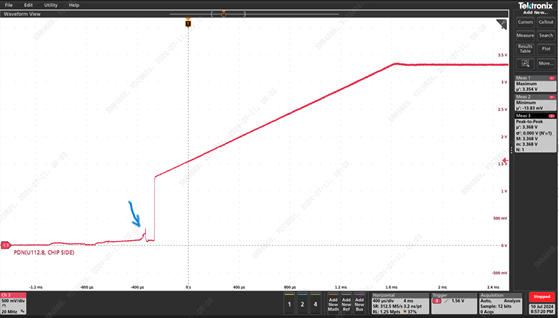

My customer reported that the voltage waveform at the PD pin is not monotonic. Please help check the schematic and analyze the reason. The client has eliminated the influence of external control signals.

Regards,

Hailiang

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi Team,

My customer reported that the voltage waveform at the PD pin is not monotonic. Please help check the schematic and analyze the reason. The client has eliminated the influence of external control signals.

Regards,

Hailiang

Hello,

How does the PDN voltage look when there are no external signals attached? (R3044 is depopulated).

How does the PDN voltage look when the external signals are attached?

Is the PDN voltage waveform causing an issue in the device performance?

Best,

Cris

Hi Chris,

How does the PDN voltage look when there are no external signals attached? (R3044 is depopulated).

How does the PDN voltage look when the external signals are attached?

Is the PDN voltage waveform causing an issue in the device performance?

The customer thinks that the non-monotonic waveform is abnormal and wants to confirm with BU whether this may be a risk.

Regards,

Hailiang

Hello,

We are currently checking with our design team and will get back to you by tomorrow.

Best,

Cris

Hello,

Our designers need some more time to look into this. In the meantime, we will check to see if we see something similar on the bench. Expect an update by Tuesday.

Best,

Cris

Hello,

We have some more questions regarding the setup:

- What is the probing method for measuring the PDN signal? Does the waveform show this behavior every time?

- The plot image you provided is a little blurry. Can you confirm the ramp time of the PDN pin? And for the VDD supply?

- PLD_CLKGEN1_PD in the scope plot is the same as PLD_CLKGEN_PD in the schematic, correct?

Best,

Cris

Hi Chris,

- What is the probing method for measuring the PDN signal? Does the waveform show this behavior every time?

Passive probes are used. Yes, this abnormal waveform appears every time.

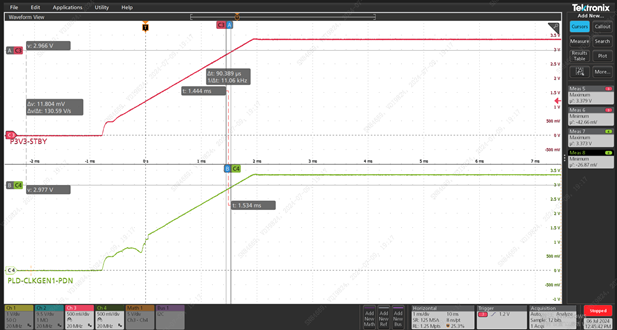

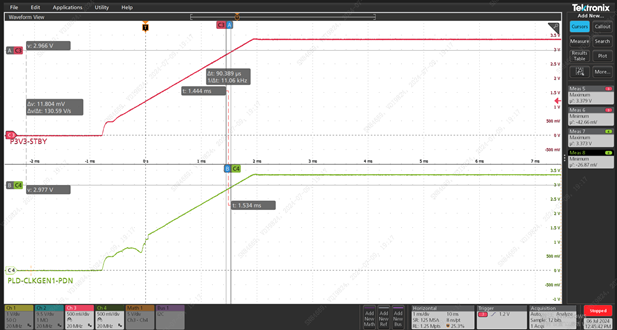

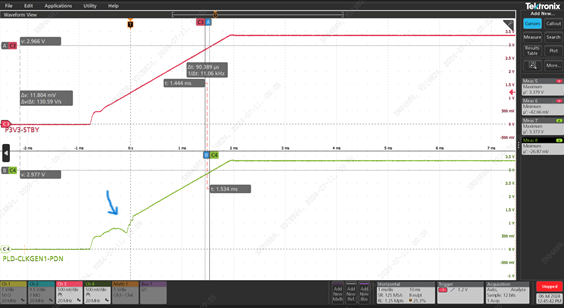

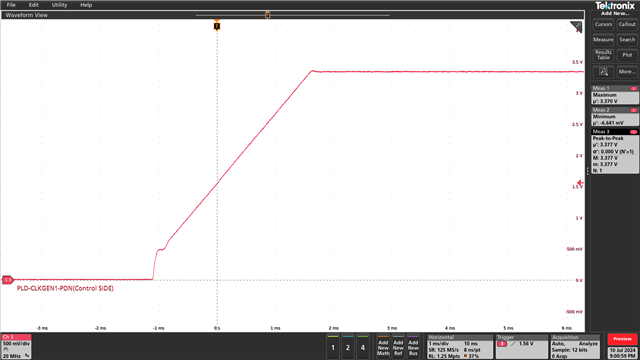

- The plot image you provided is a little blurry. Can you confirm the ramp time of the PDN pin? And for the VDD supply?

Pls refer to the below picture. VDD is powered by P3V3_STBY. The rise time of both is the same, about 2ms.

- PLD_CLKGEN1_PD in the scope plot is the same as PLD_CLKGEN_PD in the schematic, correct?

Correct.

Regards,

Hailiang

Hailiang,

Our designer is OOO today, but I will followup when he returns.

Best,

Cris

Hailiang,

Our designer recommends taking the following recommendation for a non-monotonic ramp.

Best,

Cris