Other Parts Discussed in Thread: LMX2594,

Tool/software:

Hi,

We can't serach any information for the VCO core range for LMX2582 in datasheet, and there is the table in the LMX2594 datasheet, can you provide this? thanks.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Zhang,

Good catch. This is something we should include for next DS revisions.

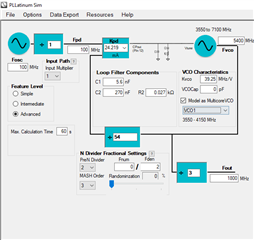

Please refer to the following from PLLatinumSim for LMX2582 device profile:

VCO1: 3550MHz-4150MHz

VCO2: 3986MHz-4579MHz

VCO3: 4481MHz-5092MHz

VCO4: 4924MHz-5596MHz

VCO5: 5535MHz-6096MHz

VCO6: 6027MHz-6632MHz

VCO7: 6555MHz-7100MHz

Regards,

Vicente

Hi, Vicente,

We have some issue for the LMX2582:

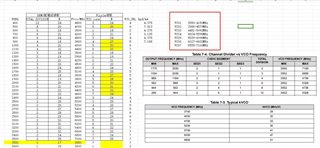

1. We use the LMX2582 based on the datasheet, and record the N and FVCO, but there are some differnet between the datasheet and PLLATINUMSIM, and we hav no idea which one is right?

2. Please advise the fasting locking time for LMX2582? We read it in the PLLATINUMSIM is more than 10us;

3. when configuring the initialization of LMX2582, I followed the instructions in the specification sheet to configure the quick lock function, but it couldn't be locked. Can you help me find out where the problem?

Hi Zhang,

The difference between your PLLatinumSim results and your TICSpro results is due to the difference in VCO frequencies

I plugged in your values and both of the following combinations can result in a 500MHz output:

Both are valid configurations but if you wish to optimize phase noise performance always use the configuration that results in the lowest N-divider value possible.

Typically we always want to use the lowest N divider by having the largest Fpd frequency - to accomplish this utilize the doubler to increase the Fpd frequency from 100MHz to 200MHz.

Please refer to the following thread on how to reduce lock time for LMX2582:

https://e2e.ti.com/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/680377/lmx2582-decrease-lock-time-possible-negative-effects

Regards,

Vicente

Regards,

Vicente

Hi Vincente,

When our company is using LMX2582, we found that during frequency switching, the lock signal output by the MUXout (LDTYPE=1) of the chip is 20us later than the measured Vtune. please advise how to solve this issue, thanks.

Hi Zhang,

I suspect the frequency might not actually be stable.

Do you have equipment capable of frequency vs time measurements?

Please refer to the last reply done by Noel to get a better idea of what I am talking about.

https://e2e.ti.com/support/clock-timing-group/clock-timing-internal/f/clock-timing---internal-forum/1384021/lmx2572lpevm-lock-time/5320658#5320658

If we look at frequency for a wide band, a device can appear "locked" while in reality the output frequency is still settling (analog settling time).

Only using a narrow band can we directly determine when the device is within the threshold for lock detect to go high.

This could explain why LD takes a bit longer to go high.

Regards,

Vicente

Hi Vicente,

What optimization methods are available for LMX2594 and LMX2582, which have high spurious frequencies of 100M on each side of the lock frequency?

Hi Zhang,

These are spurs from your PFD or ref clk (both are 100MHz).

I assume you see more spurs at 200MHz, 300MHz, etc?

You can try utilizing the input doubler or multiplier to change your phase detector frequency.

Regards,

Vicente

Hi Vincente,

We have try more multiplier to change the phase detector frequency, but there are no improve, so please advise if there are any other possible cause for this issue, thanks.

Hi Zhang,

I fear these are spurs due to OSCin.

You can try reducing the charge pump to reduce the amplitude of the spurs but I cannot guarantee this will eliminate the spurs altogether.

Regards,

Vicente