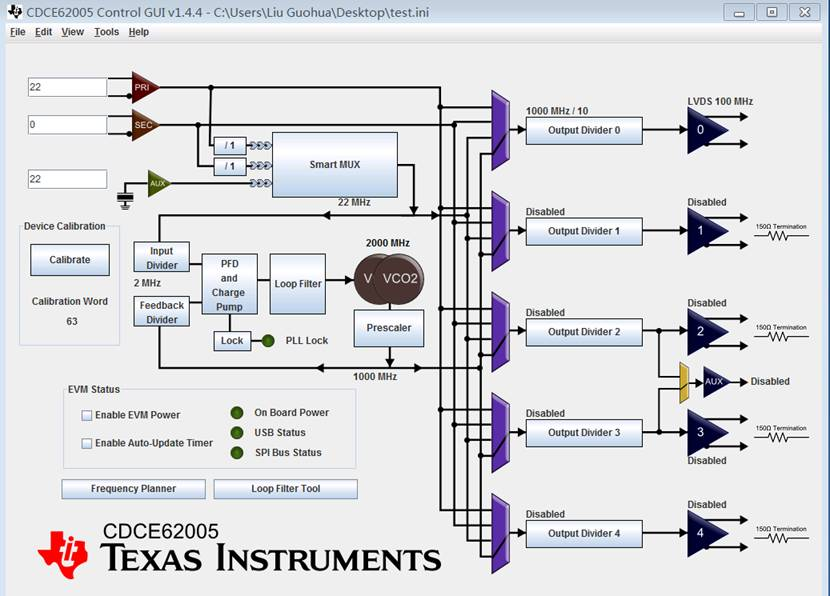

I used the “CDCE62005 Controller GUI v1.4.4" generate a register value, then I configure them

through SPI , the read back vaule of every register is right(same as the write data),

but It can't lock anyway, is there any error or whether the chip is out of work?

thanks

(I don't use 62005EVM board ,but a board designed by myself.)

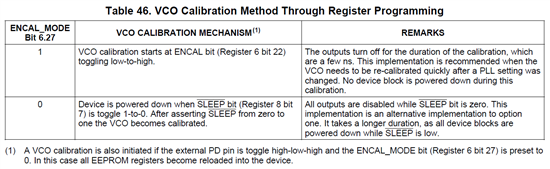

REGISTERS

0 eb0603ef

1 68ffffff

2 68ffffcf

3 68ffffef

4 68ffffff

5 fc2bff3f

6 efffc9ef

7 fd183e0f

8 ffffffff

PORTS

0 bf

1 ff

2 df

3 f9

INPUTS

PRI 22

SEC 0

AUX 22

EXTERNAL COMPONENTS

C4 4.7E-06

R4 1000

C5 2.7E-07