- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

We are integrating on the LMK5C33216 and are having some trouble understanding the intent of the datasheet. We are trying to synchronize the counters of two SYSREF outputs as described in page 57 and 58 of the datasheet. We are using the SYNC_SW via R21[6] vs the hardware GPIO. We initially tried the following sequence:

The resulting behavior was that the SYSREF outputs seemed to be turned off.

We tried a 2nd sequence as follows:

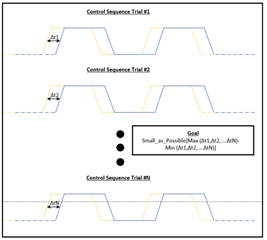

The result of this sequence was that both outputs came up and seemed to have the rising edge somewhat synchronized, but the the time delay between the rising edges of the outputs seemed to vary on the order of a few nanoseconds between sequential trials of the 2nd sequence described above.

Our goal is to have picoseconds of variation in the delay between multiple sequential trials of a control sequence. Is there any insight on the order of register writes(using SYCNC_SW) that would result in the minimum delay variation between two SYSREF outputs after running the suggested control sequence multiple times?

I created the graphic below to help illustrate the goal of the sequence.

Hi Lucas,

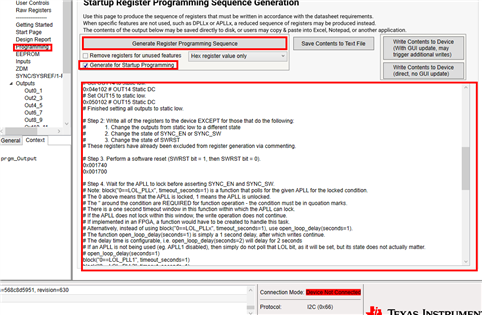

Can you please try with the sequence listed in the TICSPRO Programming page? I am in the process of updating the datasheet with more clear programming instructions.

Regards,

Jennifer

We also recommend migrating to LMK5C33216A as this is the latest silicon and has improved jitter, spur, and common-mode performance.