Other Parts Discussed in Thread: LMX1214, ADC12D1800,

Tool/software:

Hi Team,

1) How to configure/interface PLL (P/N: LMX2582RHAT) and Buffer (P/N: LMX1214) and voltage compatibility for the same.

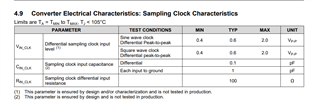

2) If one output of Buffer to FPGA in LVDS mode then can we connect another output to ADC (P/N: ADC12D1800) as well ??? and will ADC sample clock will accept the same mode??

Thanks in advance.

Regards,

Haritha