Other Parts Discussed in Thread: LMX2572

Tool/software:

Hi

I'm using the LMX2820 with instant calibration.

The Fosc is 30MHz

I'm using bias capacitor of 0.47uF, so INSTCAL_DLY = 2.5 x 30 = 75

For the first 5650MHz calibration, I'm using the N divider, but after the calibration is done, i switch to external mixer setup.

I'm getting lock time of 50uSec (7050MHz to 7150MHz). I read on the forum that people got a lock time of 10uSec and I wonder how I can improve it?

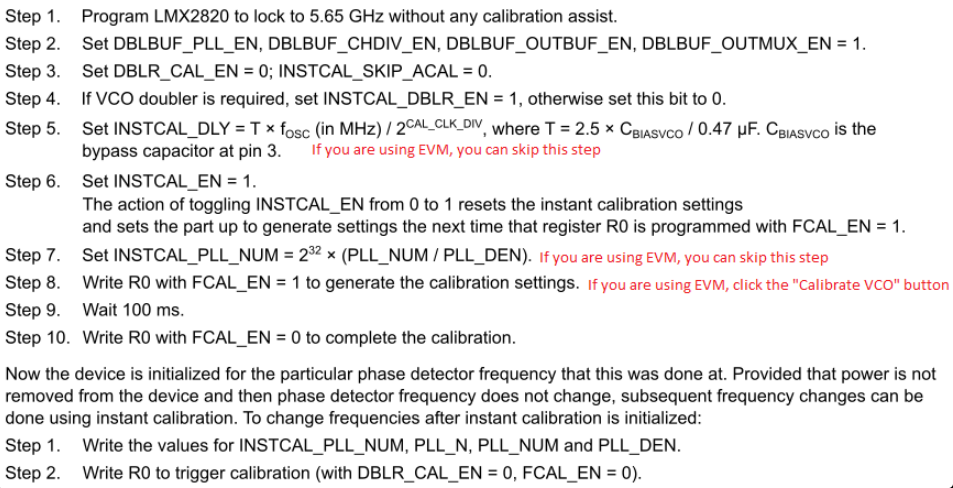

I'm following these steps for calibration:

I start with:

01,57A0

01,57A1

Then:

7A,0000

79,0000

78,0000

77,0000

76,0000

75,0000

74,0000

73,0000

72,0000

71,0000

70,FFFF

6F,0000

6E,001F

6D,0000

6C,0000

6B,0000

6A,0000

69,000A

68,0014

67,0014

66,0028

65,03E8

64,0533

63,19B9

62,1C80

61,0000

60,17F8

5F,0000

5E,0000

5D,1000

5C,0000

5B,0000

5A,0000

59,0000

58,03FF

57,FF00

56,0040

55,0000

54,0040

53,0F00

52,0000

51,0000

50,00C0

4F,0016

4E,0001

4D,0608

4C,0000

4B,0000

4A,0000

49,0000

48,0000

47,0000

46,00FE

45,0011

44,0020

43,1000

42,003F

41,0000

40,4080

3F,C350

3E,0000

3D,03E8

3C,01F4

3B,1388

3A,0000

39,0001

38,0001

37,0002

36,0000

35,0000

34,0000

33,203F

32,0080

31,0000

30,4180

2F,0300

2E,0300

2D,5555

2C,5555

2B,4000

2A,0000

29,0000

28,0000

27,C000

26,0000

25,0500

24,00BC

23,3100

22,0010

21,0000

20,1001

1F,0401

1E,B18C

1D,318C

1C,0639

1B,8001

1A,0DB0

19,0624

18,0E34

17,1102

16,E2BF

15,1C64

14,272C

13,2120

12,0010

11,15C0

10,171E

0F,2001

0E,3001

0D,0038

0C,0408

0B,0602

0A,0000

09,0005

08,C802

07,0000

06,0A43

05,0032

04,4204

03,0041

02,8097

00,4030

Wait 100mSec

00,4020

Now the calibration is done, the PLL is locked on 5650MHz.

I switch to external mixer and 7050MHz output:

39,0000

0F,2601

2C,0000

2D,0000

24,00EB

2A,0000

2B,0000

00,4020

And then to 7150MHz output:

2C,5555

2D,5555

24,00EE

2A,0000

2B,4000

00,4020

Thank you