Tool/software:

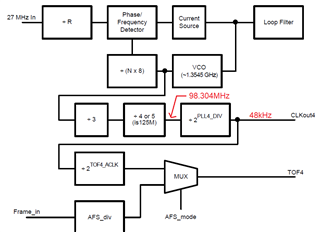

I want to generate 48MHz clock on PLL4 with 27MHz input from PLL1. Is PLL4 capable of being setup to operate at 48MHz?

I've reviewed AN2108 example to generate 44.1KHz but the values that were calculated and presented in the paper do not actually generate 44.1KHz. Is there an error in that paper?