Tool/software:

II was wondering if you had any advice on generating a 156.25 MHz signal synchronized to a PPS signal using the LMK06318B (or another part if one is better suited). I have available as inputs the PPS signal and a configurable higher-frequency signal up to 62.5 MHz that is synchronized to the PPS. The high frequency signal has the limitation that period has to be an even number of nanoseconds that is 16 ns or greater.

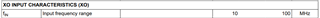

One option is to use the configurable high frequency signal as XO input and multiply it up to 156.25 MHz. Set it to, for instance, 31.25 Mhz and multiply it by 5.This just uses the APLL.

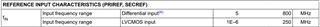

Another option, and probably more typical for this chip, is to use the PPS as reference input for the DPLL, use the synchronized high frequency signal as XO, and generate the 156.25 Mhz signal using APLL1. I see it would also be possible to generate a PPS output signal using zero-delay mode.

Any advice on the relative merits of these 2 approaches? The degree to which the 156.25 MHz signal is synchronized to the PPS is the important criterion.