Tool/software:

Hi,

We have a customer requirement to interface the LMX1214 clk buff SPI -> opto ISO6721FB -> FPGA

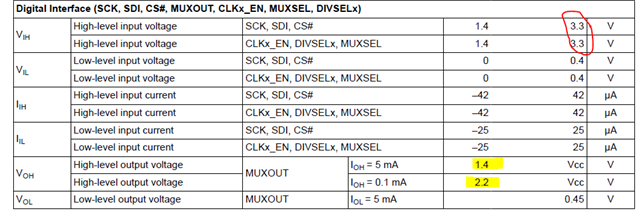

- In the LMX datasheet, 2 different values are given for muxout (SPI SDO). Now which VoH value needs to be considered for voltage loading analysis?

- shouldn't the ViH max be 2.5V?

Thanks