Part Number: LMX1204

Tool/software:

We want a fixed phase relationship between CLKOUT and SYSREF generated by LMX1204. When using LMX1204 for clock and sysref synchronization, the phase cannot be fixed.

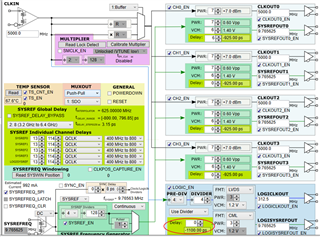

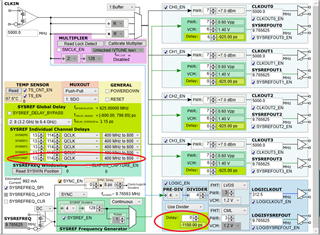

Four SYSREFOUT, one LOGICLKOUT and one LOGISYSREFOUT are generated by dividing the CLKIN of LMX1204, and four CLKOUT with the same frequency as CLKIN are generated by the buffer function.

In the current configuration, SYSREF uses the continuous mode, and SYSREFREQ has a single pulse LVDS level input through our control.

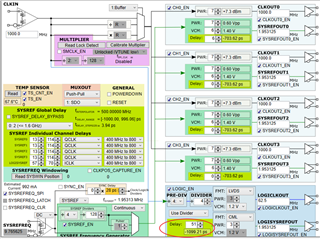

After LMX1204 generates four CLKOUTs, four SYSREFOUTs, one LOGICLKOUT and one LOGISYSREFOUT, we modify the configuration as follows:

1) Set the SYSREFREQ_N level to 1.4V, set the SYSREFREQ_P level to 1.0V

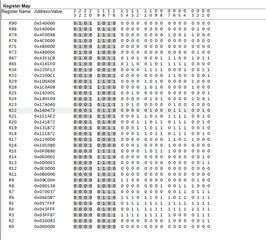

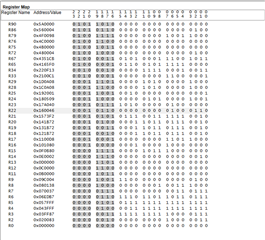

2) Modify the LMX1204 register:

0E,0100

09, E004

0F, 0B84

3) Set the SYSREFREQ_N level to 1.0V, set the SYSREFREQ_P level to 1.4V

However, after this configuration, the fixed phase relationship between SYSREFOUT, LOGISYSREFOUT and CLKOUT cannot be maintained.