Tool/software:

Hi,

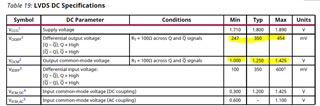

We want to interface the FPGA LVDS output to the SYNC pin. Based on below FPGA LVDS output spec, both common mode and differential seem to be out of spec.

For FPGA outputs from 1V to 1.425V. VCM of SYNC pin starts from 1.2-2V.

Similarly Vodiff of FPGA is 247 to 454mV. But for CB it starts from 0.6/0.8V

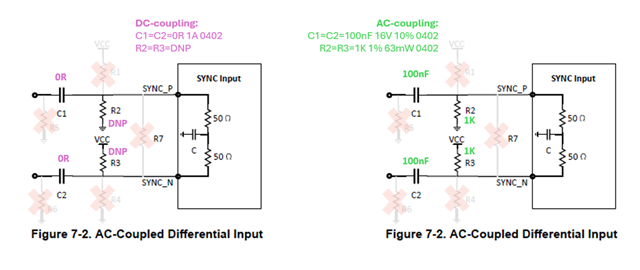

Can you pls suggest how these signals are to be coupled to the FPGA?