Tool/software:

Hi,

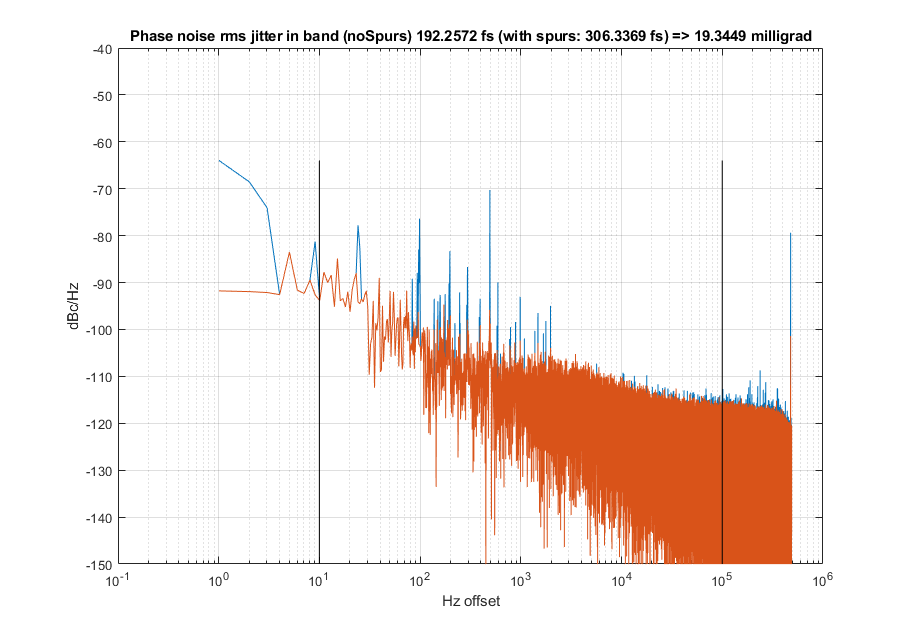

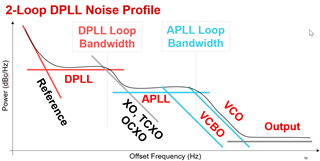

We have some troubles with phase noise spurs in the output of the APLL3/DPLL3. When only the APLL3 is active the output phase noise is good, however when we are enabling the DPLL3 then we get some significant phase noise spurs in the 50Hz - 1000Hz offset band. The additional phase noise that occurs when enabling the DPLL is around ~250fs rms due to the spurs.

Our settings is: f_vco = 25MHz, f_ref = 10 MHz, DPLL_BW = 1 Hz, f_TDC = 1 MHz, f_out = VCO3/4 = 614.4MHz (Different DPLL_BW and f_TDC lead to similar results, with slightly different spur frequencies and amplitudes)

We are using TICSPro to calculate the register values.

Is this expected behavior? Or how could we mitigate this issue? For us the 10Hz to 100kHz offset band is of most importance.

Thanks a lot for any help and regards,

Christoph