Other Parts Discussed in Thread: LMX2487

Tool/software:

Hello,

My customer, Tarana Wireless, provided some information regarding their clock tree for a new program they're developing. Can you take a look and work with me to help provide a few devices or a system-level recommendation for them from TI? Happy to support this ask via a call or however is the team is able to support at this time:

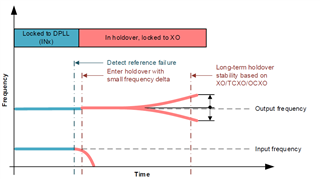

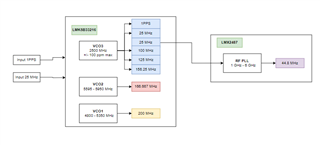

I'm looking to synthesize a 44.8MHz LVDS clock with <60fs jitter from a device that I can lock to a 1PPS or 1MPPS and 25MHz reference with automatic failover to a local XO. I would also like to synthesize 1PPS, 25MHz, 100MHz, 125MHz, 156.25MHz, 166.667MHz and 200MHz but the jitter requirements are only in the 250fs range or greater. I can also synthesize them separately if necessary.

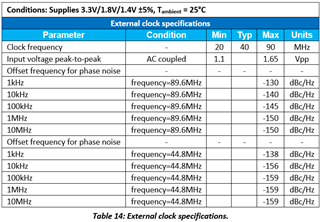

One thing to note is that the jitter specifications are estimates based on the phase noise requirements of our system, however the RMS value is integrated over a non-standard frequency range.

Please see the datasheet of the ASICs that will be driven by this 44.8MHz clock source:

Please let me know if we are able to support this ask! Thanks very much,

Owen