Other Parts Discussed in Thread: LMX2594, LMX2820

Tool/software:

Hi ALL,

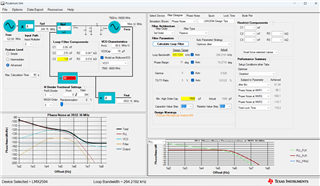

I would like to make a continuous clock with a square wave for the 1.92MHz Clock OUTPUT using the LXK04832 PLL IC, but a pulse-shaped waveform is being output as shown in the attached photo.

Please help me as to why it is output like this. Attached is the XX.TCS file

Thanks.

Second_LMK04832_config_240924.tcs