Tool/software:

Hello,

I would like to verify a high-level proposed architecture before producing PCBs.

Background:

Our embedded system contains a uBlox LEA-M8F GPS module, which has both a standard 1PPS timing reference signal (derived from GPS), as well as a 30.72MHz disciplined frequency reference derived from a VCTCXO & PLL internal to the GPS module (clock specs here).

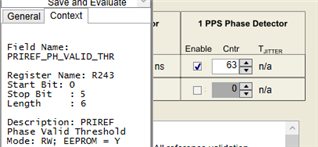

Proposal: Feed the uBlox 1PPS signal into the PRIREF input of LMK05318B, and feed the uBlox 30.72MHz signal into the XO input of the LMK05318B. Upon loss of GPS lock, the 30.72MHz clock enters holdover mode until GPS lock is reacquired. 30.72MHz is one of the recommended XO frequencies, we will verify levels match, ensure correct transmission line termination, etc. I've already created the configuration in TICS PRO that meets all of our input/output frequency requirements, so I'm mostly double checking there's not some obscure requirement I'm missing (e.g. that the XO and PRIREF be derived from separate sources, etc.).

Any feedback is appreciated, thank you.