Tool/software:

Hello,

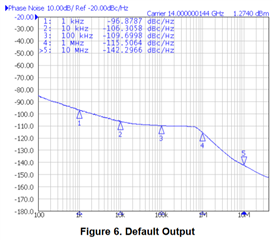

I'm struggling to recreate the default output shown in figure 6 of the LMX2694EPEVM Evaluation Instructions, also shown below:

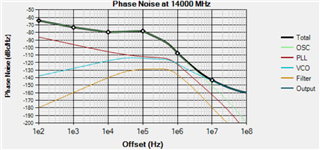

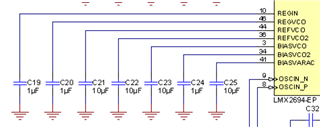

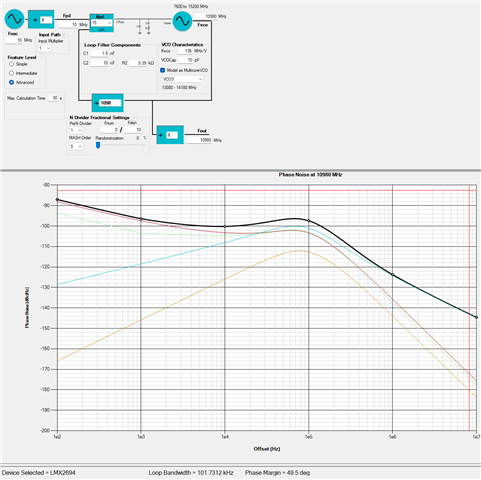

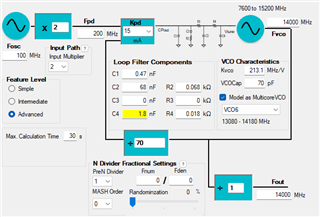

I've configured PLLatinum sim with the default loop filter that comes installed on the eval board and verified that the simulated phase noise matches what the evaluation instructions says I should be getting:

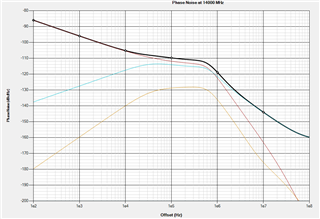

I've followed the EVM Connection Diagram shown on figure 1 of the user guide and am using a high quality signal generator at an appropriate input level to supply the necessary 100 MHz reference clock needed for this default configuration. I've verified that it shouldn't be interfering with my measurement as the phase noise of this tone is noticeably below the overall phase noise as simulated by the PLLatinum sim. It is higher at the 100Mhz range, but I'm primarily interested in the overall phase noise up to 10Mhz:

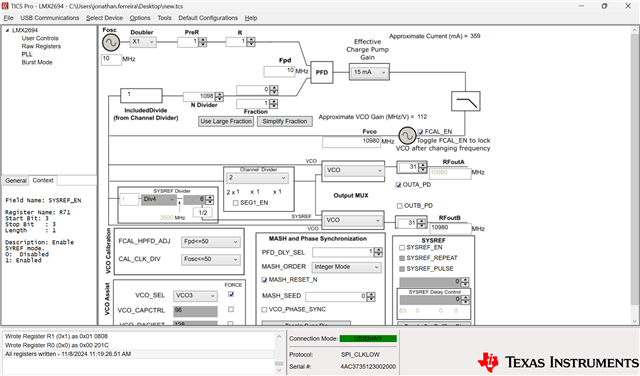

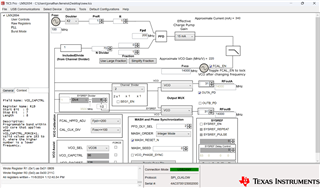

I've configured my TICS Pro instance to be identical to the PLLatinum sim but I'm getting a grossly spurious output:

I don't think there's anything wrong with my setup (verified that the input reference is sufficiently noise free, eliminating power supply noise to eval board by using LDO, onboard LED turns green which indicates that PLL is locking) and the only thing I see potentially leading to such a degraded output signal is in how I've configured TICS Pro. Is there anything I've missed in my setup or replicating my PLLatinum Sim configuration in TICS Pro that could be leading to such a grossly degraded output signal? If not, then what else could explain such behavior?