Tool/software:

Hello:

At present, we are using two-channel lmx2595 for phase adjustment and manual RAMP application. I hope you can help me to answer the following questions:

Phase regulation:

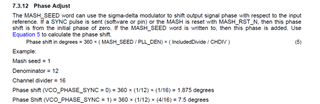

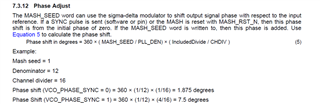

1、1According to the calculation formula in manual 7.3.12, the calculated result is not consistent with the actual output result, and the actual adjustment Angle is much smaller than the value set by me. But when I set it to 90 degrees, the actual Angle is about the same, and I want to know what's the problem

2、I noticed in 7.3.12 that the value of MASH_SEED is less than PLL_DEN, but in my actual test, values greater than PLL_DEN also have phase changes. Is there any effect when MASH_SEED is greater than PLL_DEN?

3, when using the phase adjustment function is PLL_DEN is there any restrictions? When I set PLL_DEN to 1000000000, I found that no matter how I set the MASH_SEED output phase, it didn't change.

- In practice, I hope that when SYNC=0, I can modify the phase difference of MASH_SEED two ways 2595 to be absolute value instead of adding some Angle to the current one.

TIP: The FOSC I use is 10M, and when both 2595s output 200M for phase adjustment, PLL_DEN is set to 2083333

Manual RAMP:

When I use the manual RAMP mode, the RAMP waveform is not stable, but when I exit the RAMP mode quickly and re-enter the RAMP waveform can be normal, and then restart the RAMP modulation can be normal output. It seems that 2592 could not parse my drive waveform correctly at the beginning, please help me analyze what caused it

This is where I drive the waveform CLK at a frequency of 27.5KHZ and DIR pulls up every 138th pulse

This is the waveform that starts modulating after power-on

This is a normal modulated waveform

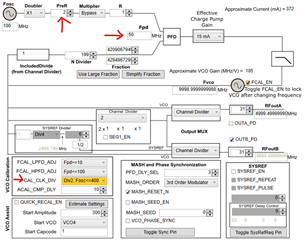

Here are my chip setup parameters:

|

LMX2595_R112 |

, |

0x0000 |

|

LMX2595_R111 |

, |

0x0000 |

|

LMX2595_R110 |

, |

0x0000 |

|

LMX2595_R109 |

, |

0x0000 |

|

LMX2595_R108 |

, |

0x0000 |

|

LMX2595_R107 |

, |

0x0000 |

|

LMX2595_R106 |

, |

0x0000 |

|

LMX2595_R105 |

, |

0x0021 |

|

LMX2595_R104 |

, |

0x0000 |

|

LMX2595_R103 |

, |

0x0000 |

|

LMX2595_R102 |

, |

0x3F00 |

|

LMX2595_R101 |

, |

0x0011 |

|

LMX2595_R100 |

, |

0x0000 |

|

LMX2595_R99 |

, |

0x0000 |

|

LMX2595_R98 |

, |

0x0400 |

|

LMX2595_R97 |

, |

0x0888 |

|

LMX2595_R96 |

, |

0x0000 |

|

LMX2595_R95 |

, |

0x0000 |

|

LMX2595_R94 |

, |

0x0000 |

|

LMX2595_R93 |

, |

0x0000 |

|

LMX2595_R92 |

, |

0x0000 |

|

LMX2595_R91 |

, |

0x0000 |

|

LMX2595_R90 |

, |

0x0000 |

|

LMX2595_R89 |

, |

0x0000 |

|

LMX2595_R88 |

, |

0x0000 |

|

LMX2595_R87 |

, |

0x0000 |

|

LMX2595_R86 |

, |

0x9999 |

|

LMX2595_R85 |

, |

0x9C19 |

|

LMX2595_R84 |

, |

0x0001 |

|

LMX2595_R83 |

, |

0x0000 |

|

LMX2595_R82 |

, |

0x6400 |

|

LMX2595_R81 |

, |

0x0000 |

|

LMX2595_R80 |

, |

0x0000 |

|

LMX2595_R79 |

, |

0x0080 |

|

LMX2595_R78 |

, |

0x0101 |

|

LMX2595_R77 |

, |

0x0000 |

|

LMX2595_R76 |

, |

0x000C |

|

LMX2595_R75 |

, |

0x0800 |

|

LMX2595_R74 |

, |

0x0000 |

|

LMX2595_R73 |

, |

0x0FFF |

|

LMX2595_R72 |

, |

0x0000 |

|

LMX2595_R71 |

, |

0x0001 |

|

LMX2595_R70 |

, |

0xC350 |

|

LMX2595_R69 |

, |

0x0000 |

|

LMX2595_R68 |

, |

0x03E8 |

|

LMX2595_R67 |

, |

0x0000 |

|

LMX2595_R66 |

, |

0x01F4 |

|

LMX2595_R65 |

, |

0x0000 |

|

LMX2595_R64 |

, |

0x1388 |

|

LMX2595_R63 |

, |

0x0000 |

|

LMX2595_R62 |

, |

0x0322 |

|

LMX2595_R61 |

, |

0x00A8 |

|

LMX2595_R60 |

, |

0x0000 |

|

LMX2595_R59 |

, |

0x0001 |

|

LMX2595_R58 |

, |

0x1001 |

|

LMX2595_R57 |

, |

0x0020 |

|

LMX2595_R56 |

, |

0x0000 |

|

LMX2595_R55 |

, |

0x0000 |

|

LMX2595_R54 |

, |

0x0000 |

|

LMX2595_R53 |

, |

0x0000 |

|

LMX2595_R52 |

, |

0x0820 |

|

LMX2595_R51 |

, |

0x0080 |

|

LMX2595_R50 |

, |

0x0000 |

|

LMX2595_R49 |

, |

0x4180 |

|

LMX2595_R48 |

, |

0x0300 |

|

LMX2595_R47 |

, |

0x0300 |

|

LMX2595_R46 |

, |

0x07FD |

|

LMX2595_R45 |

, |

0xC8DF |

|

LMX2595_R44 |

, |

0x1FA3 |

|

LMX2595_R43 |

, |

0x0000 |

|

LMX2595_R42 |

, |

0x0000 |

|

LMX2595_R41 |

, |

0x0000 |

|

LMX2595_R40 |

, |

0x0000 |

|

LMX2595_R39 |

, |

0xE100 |

|

LMX2595_R38 |

, |

0x05F5 |

|

LMX2595_R37 |

, |

0x8304 |

|

LMX2595_R36 |

, |

0x03E8 |

|

LMX2595_R35 |

, |

0x0004 |

|

LMX2595_R34 |

, |

0x0000 |

|

LMX2595_R33 |

, |

0x1E21 |

|

LMX2595_R32 |

, |

0x0393 |

|

LMX2595_R31 |

, |

0x03EC |

|

LMX2595_R30 |

, |

0x318C |

|

LMX2595_R29 |

, |

0x318C |

|

LMX2595_R28 |

, |

0x0488 |

|

LMX2595_R27 |

, |

0x0002 |

|

LMX2595_R26 |

, |

0x0DB0 |

|

LMX2595_R25 |

, |

0x0C2B |

|

LMX2595_R24 |

, |

0x071A |

|

LMX2595_R23 |

, |

0x007C |

|

LMX2595_R22 |

, |

0x0001 |

|

LMX2595_R21 |

, |

0x0401 |

|

LMX2595_R20 |

, |

0xE048 |

|

LMX2595_R19 |

, |

0x27B7 |

|

LMX2595_R18 |

, |

0x0064 |

|

LMX2595_R17 |

, |

0x0064 |

|

LMX2595_R16 |

, |

0x0080 |

|

LMX2595_R15 |

, |

0x064F |

|

LMX2595_R14 |

, |

0x1E70 |

|

LMX2595_R13 |

, |

0x4000 |

|

LMX2595_R12 |

, |

0x5001 |

|

LMX2595_R11 |

, |

0x0018 |

|

LMX2595_R10 |

, |

0x10D8 |

|

LMX2595_R9 |

, |

0x0604 |

|

LMX2595_R8 |

, |

0x2000 |

|

LMX2595_R7 |

, |

0x40B2 |

|

LMX2595_R6 |

, |

0xC802 |

|

LMX2595_R5 |

, |

0x00C8 |

|

LMX2595_R4 |

, |

0x0A43 |

|

LMX2595_R3 |

, |

0x0642 |

|

LMX2595_R2 |

, |

0x0500 |

|

LMX2595_R1 |

, |

0x0808 |

|

LMX2595_R0 |

, |

0x241C |

你好:

目前我们在使用两路lmx2595做相位调节及手动RAMP的应用,遇到以下问题希望能帮我解答一下:

相位调节:

- 根据手册3.12的计算公式,计算的结果与实际输出的结果并不一致,实际调节的角度要比我设置值小很多。但当我设置为90°时实际角度又差不多,我想知道是什么问题引起的

- 我注意到3.12中说MASH_SEED的值要小于PLL_DEN ,但我实际测试时大于PLL_DEN的值也是有相位改变的 ,当MASH_SEED大于PLL_DEN时是有什么影响吗?

- 当使用相位调节功能是PLL_DEN是有什么限制吗?当我PLL_DEN 设置为1000000000时发现无论我怎么设置MASH_SEED 输出相位都没有改变。

- 实际使用中,我希望在SYNC=0时,当修改MASH_SEED两路2595的相位差是绝对值而不是在当前的基础上累加一定角度,这种能实现吗?

tip:我使用的FOSC为10M,当两路2595都输出200M做相位调节时PLL_DEN设置为2083333

手动ramp:

当我使用手动ramp模式时,ramp波形并不能稳定,但当我快速退出RAMP模式并重新进入后RAMP波形又能正常,而且之后重新开始ramp调制也能正常输出。感觉像是一开始的时候2592并不能正确的解析我的驱动波形,请帮我分析下是什么问题导致的

这是我的驱动波形 CLK的频率为27.5kHz每第138个脉冲DIR会拉高