Tool/software:

Hello,

I have query regarding the PLLatinum simulation.

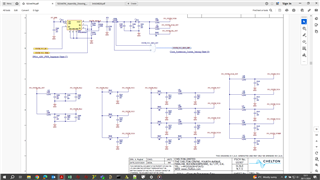

We are using LMK04828B with external VCXO option in the PLLatinum simulation and have come up with following values for both PLL1 and PLL2 and used the same the filter values connected at CPout1 and CPout2 as shown below.

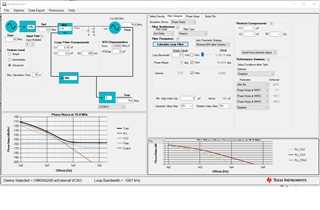

But regarding PLL1 specifically, when I am loading the device with external VCXO, PLLatinum Sim loads with KVCO and VCOCap values as shown below (Charge pump current (Kpd), input and output frequencies are what we are using in our design currently so are correct).

Default KVCO value is 0.0025 MHz/V when loading up the PLLatinum Sim as above.

Default VCOCap value is 0pF when loading up the PLLatinum Sim as above.

But as we are using an external VCXO of which datasheet link I have mentioned it below:

After looking into an external VCXO datasheet I have changed both VCO characteristics values (KVCO and VCOcap) as shown below.

I have converted 25ppm tuning sensitivity to Hz (from VCXO datasheet) and used that value in KVCO field and I thought VCOCap would be the output capacitance and used 15pF from the VCXO datasheet and placed it in VCOCap field below.

After using these values we have different loop filer 2nd order values to the one from default values and these values we have used in our design.

I have now following queries,

1. Do we just leave both KVCO and VCOCap values as it is when PLLatinum Sim first load up after selecting LMK04828 w/external VCXO?

2. How would we can get the VCOCap value?

3. What I have done to find the loop filter values by changing the KVCO and VCOCap values as shown in second screenshot is right or wrong? and what could I do to make it right?

Thanks,