Other Parts Discussed in Thread: TMAG5273

Tool/software:

Hi team,

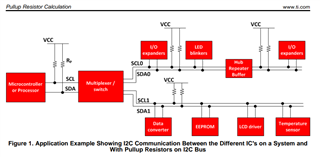

I am considering using 21 LMK1C1108s to distribute SCLs from one FPGA to 161 TMAG5273s.

Q1. Do I need a pull-up for each output? (It enters TMAG5273)

Should it be connected as shown in the figure below?

https://www.ti.com/lit/an/slva689/slva689.pdf

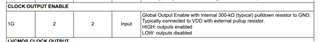

Q2. Do I need a pull-up for 1G? (Datasheet say" Typically connected to VDD with external pullup resistor", but just to confirm.)

Regards,

Hiromu