Other Parts Discussed in Thread: LMK04610, LMK01000

Tool/software:

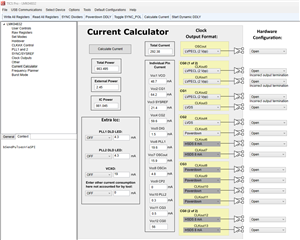

is the power number listed for my LMK04832 configuration in Clock Architect only the Core power or does this include the outputs power as well? I cannot tell if the LVPECL and LVDS currents that get sourced to their loads are taken into account here.