Other Parts Discussed in Thread: AM6411

Tool/software:

Hello,

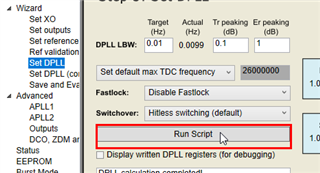

I am trying to output a 27MHz clock from lmk5b12204 PLL2, but the read value of R14 Register is 0xD0 and the DPLL is not locked.

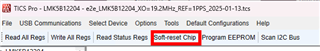

I am loading the attached tcs file with TICS Pro and writing the registers of lmk5b12204 via I2C.

I would like to find out why the DPLL does not lock. Could you please check if there are any problems with the TICS Pro settings or the register write values of lmk5b12204?

For reference, when the DPLL is not locked, R13 = 0x00, R14 = 0xD0, R167 = 0x00, and R411 = 0x00.

PPS is output from the CPU.

CPU:AM6411

Clock Synthesizer: lmk5b12204

xo :19.2MHz 0.5ppm

Thank you,

Tanaka