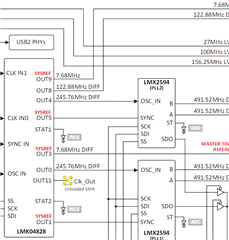

Other Parts Discussed in Thread: LMK04828, USB2ANY,

Tool/software:

Hi Team,

Can you please help us with our customer inquiry below.

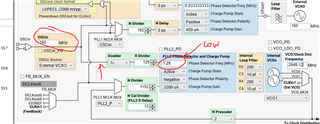

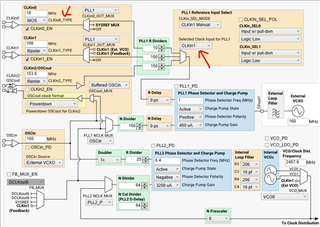

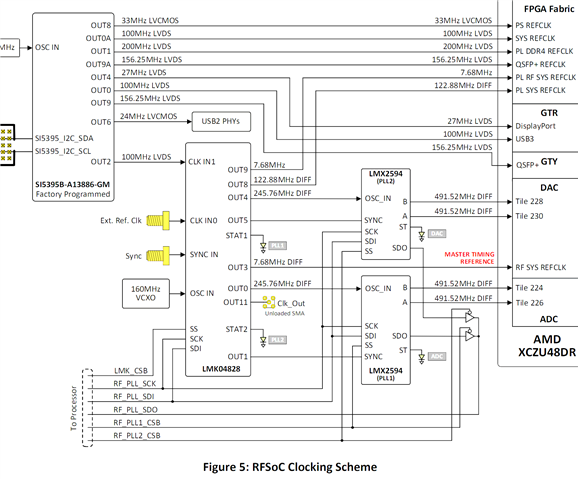

We are trying to enable CLK_IN_0 (image 1) to have a 10MHz signal sync with the device. Looking at TICS and PYNQ forums

https://discuss.pynq.io/t/xrfclk-configuration-lmk04828-using-external-10mhz-reference-clock/5562/12

https://e2e.ti.com/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1229913/lmk04828-taking-driving_clock-from-another-input-pin-and-i-can-t-figure-out-which-one/4661353#4661353

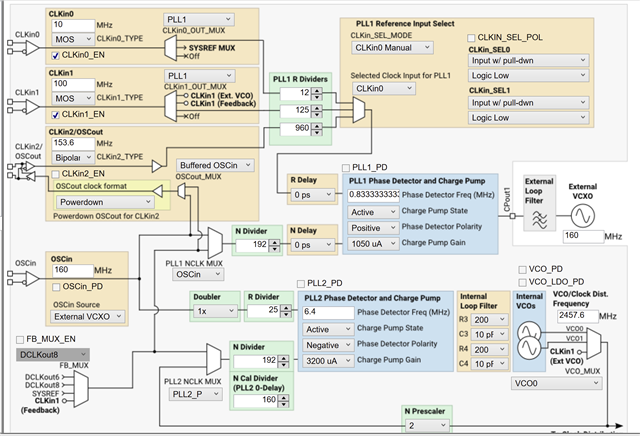

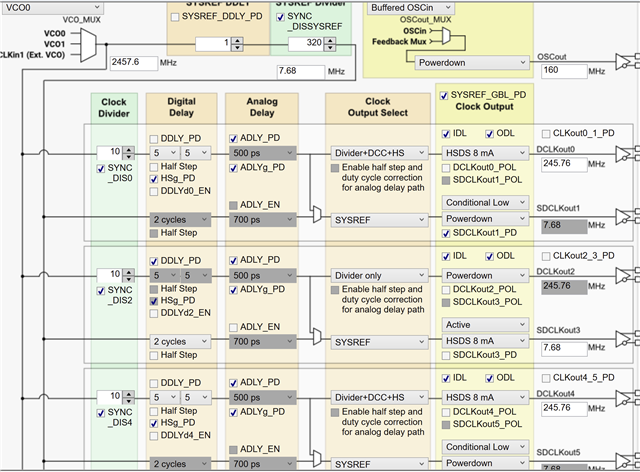

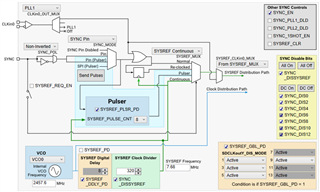

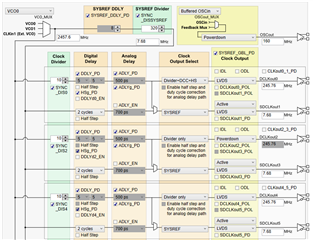

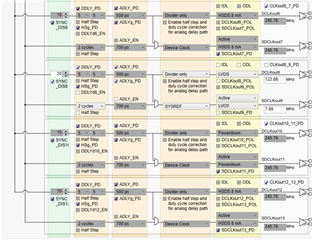

I came across 3 different solutions. Provided are .txt files for hex import for each. Using TICS PRO, I am trying to configure our board to have a 10MHz external clock control while disabling OSCin internal referance clock. The other frequencies on the image should remain the same. I don't want to program the board by using USB2ANY cable with any of these .txt files for hex import because we don't have the default LMK04828 .tcs file for the RFSoC4x2. Can you please help us on how we can proceed? We are really stuck and Real Digital didn't provide us the default LMK04828 file for the board.

Regards,

Danilo