Other Parts Discussed in Thread: LMK04832

Tool/software:

Hi Team.

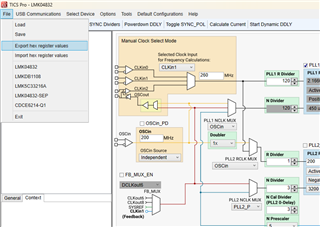

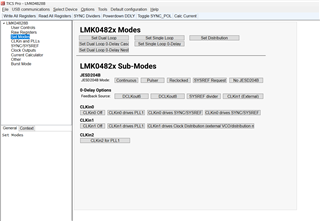

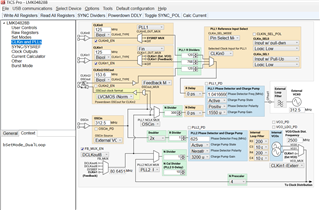

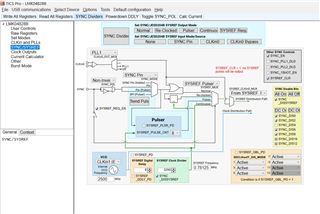

We are working on ADC - DAC Loopback on FMC Evaluation board, which is having a clock generator - LMK04828 & a transceiver on it.

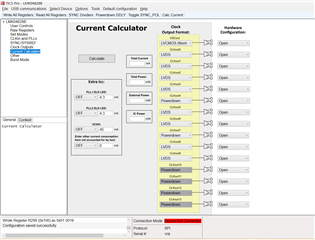

For this we need a register dump (register write sequence) to configure the LMK04828 to get the desired clocks.

We need the following clocks with mentioned frequencies to configure on LMK04828:

DCLKOUT0, DCLKOUT0* = 100 MHz

SDCLKOUT1, SDCLKOUT1* = 100 MHz

DCLKOUT6, DCLKOUT6* = 125 MHz

NOTE : We are using OSCIN (Pin 43 of LMK04828) as the reference clock(which is 48 MHz clock oscillator) for LMK04828.

We are attaching the LMK04828 IC chip Image for reference.

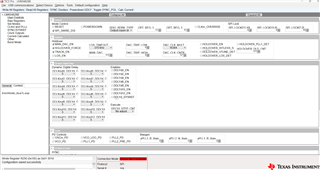

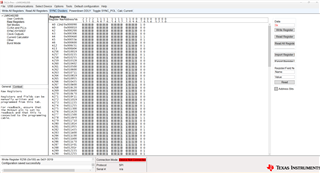

We require the register dump for LMK04828 to configure the above clocks to implement the ADC - DAC loopback for our requirement.

Please kindly proved us the register dump (register write sequence) like 0x000090 where MSB 2 Bytes 0000 represents address of register & LSB Byte represents Data to write into that particular register.

We will look forward for your reply.