Tool/software:

According to the TICS export register and sequence, it still cannon lock to a defined frequency, Vt voltage 0.37V at power on, 0.04V after writing...

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Jac,

The configuration looks good.

Are you using your loop filter or using eval board default loop filter?

Is the reference clock a TCXO with clipped sine wave output? How did you connect it to the synthesizer?

Hi Jac,

OSCin schematic is fine, if you share this signal with other device via C329, make sure the voltage is still sufficient at OSCIN_P pin.

The reason of unlock is probably due to the loop filter.

According to you configuration and loop filter, phase margin of the loop is 19.38deg, which means the loop is not stable.

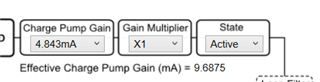

You can do a quick check by increasing the charge pump gain. Below setting will bring the phase margin to 46.6deg.