Part Number: LMX1204

Tool/software:

Dear Specialists,

My customer is evaluating LMX1204 and has questions.

I would be grateful if you could advise.

---Question

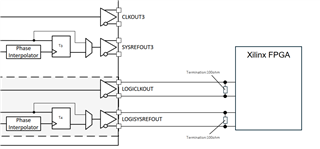

As shown in the attached configuration, the LOGICLKOUT of the LMX1204 is connected to the FPGA.

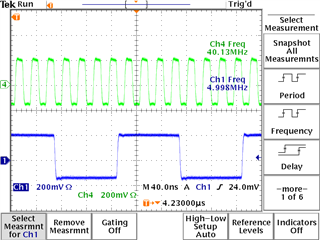

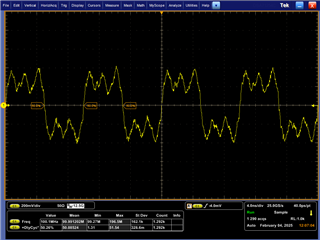

When observing the LOGICLKOUT waveform at the FPGA end, large ringing was observed.

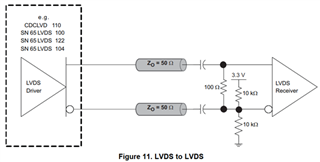

-Set the output format of both LOGICLKOUT and LOGISYSREFOUT to LVDS.

-Connected to FPGA by DC coupling (direct connection).

-Install a 100Ω termination resistor on the FPGA side (receiving end).

When observing the LOGICLKOUT waveform at the FPGA end, ringing like the one shown below occurs.

Q1:

According to the circuit diagram in the LMX1204EVM User's Guide

The output is output to the SMA connector by AC coupling (0.1uF).

Is AC coupling necessary for LVDS output?

※Does this mean DC coupling cannot be used?

Q2:

If DC coupling is possible, is it sufficient to only use 100 Ω termination on the receiving side as shown in the attached diagram?

Q3:

As far as I understand, the only register settings related to LVDS output are the output format and VCM settings.

Are there any other settings that need to be set?

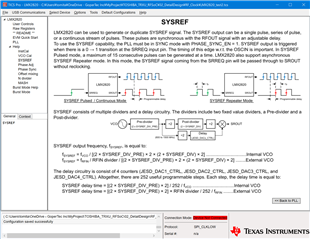

I have attached the configuration file to this email, so if there are any errors in the settings, I would appreciate it if you could let me know.

Q4:

If there are no problems with the configuration, connections, or settings, what do you think could be the cause of the severe ringing as shown in the attached diagram?

However, when I modified this configuration to use LVPECL (AC coupling), the ringing did not occur and the clock waveform was fine, so I do not think there is a problem with the wiring pattern on the printed circuit board.

ーーー

I appreciate your great help in advance.

Best regards,

Shinichi