Tool/software:

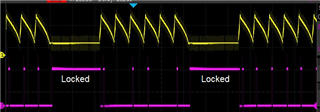

I have a PLL application where I use the ramping function. I read out cyclic (every 10us) the rb_LD_VTUNE (R110[10:9]) and set a pin when it the state is locked. In the following picture you see the channels:

yellow: PLL Vtune

red: Lock detect pin (active high)

blue: nCS Chip select of reading the register R110

I have expected that the PLL is locked while the vTune down-ramp. As you can see this is not the case. Can anybody explain why it behaves like that?