Hi there,

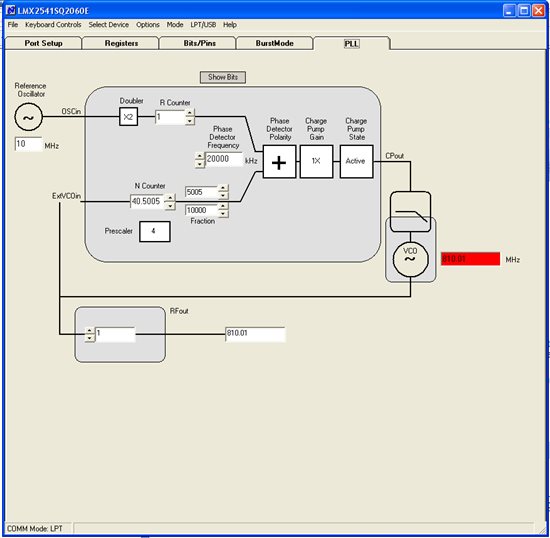

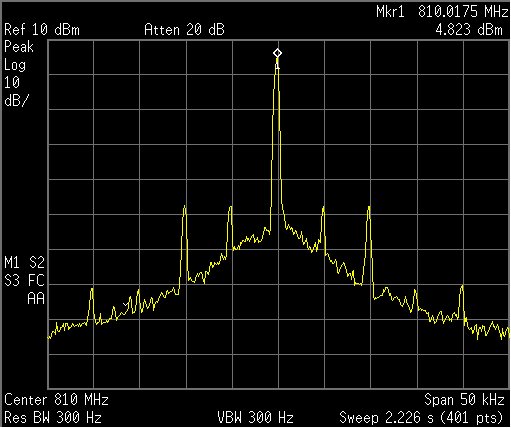

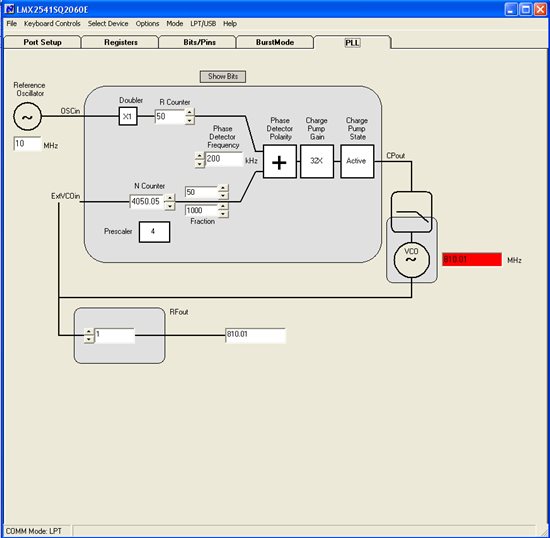

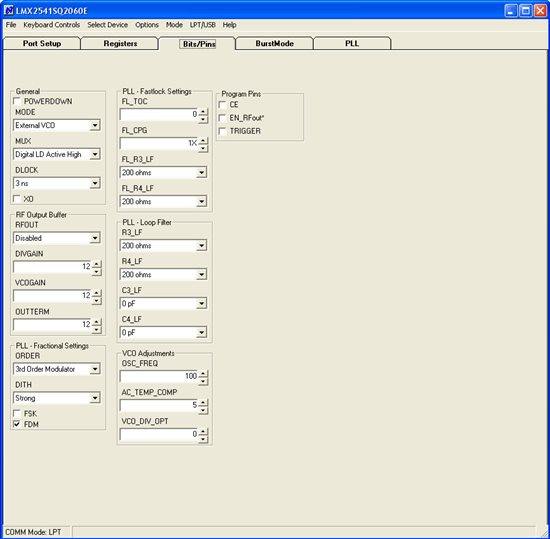

I am working on a project which uses the LMX2541 PLL+VCO chip to generate an ultra-low noise carrier frequency at 810.01 MHz. I am using an external VCO working from 805 MHz to 815 MHz and an external reference XO working at 10 MHz (The LMX2541 is working in External VCO mode.). The RFoutEN is turned off and I am extracting the 810.01 MHz signal directly from the VCO chip. The LMX2541's registers are configured as shown below.

R7 0x00000017

R13 0x0000008D

R12 0x0000001C

R9 0x28001409

R8 0x0111CE58

R6 0x001F3306

R5 0xA0000005

R4 0x00001644

R3 0x013A7F13

R2 0x04003E82

R1 0x00000321

R0 0x0032FD20

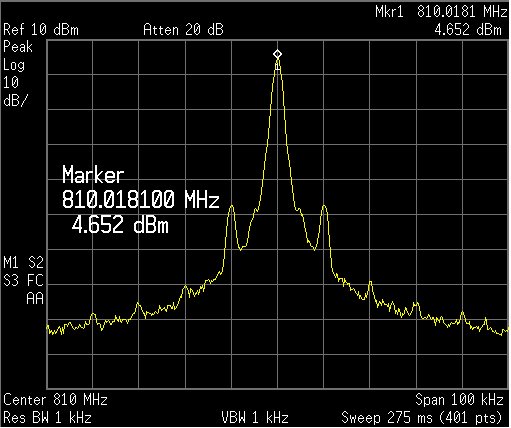

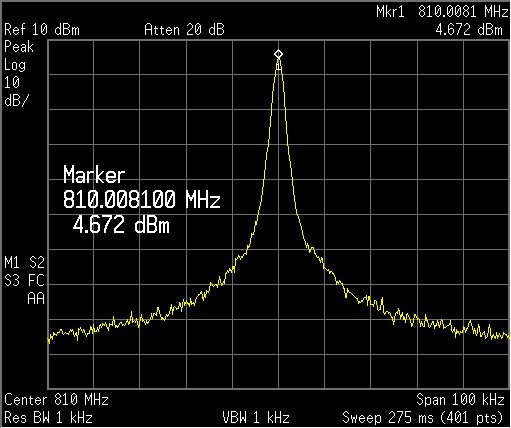

The purpose of this project is to achieve an ultra-low phase noise and fractional spurs. However, by using the above configurations, high phase noise and fractional spurs can be found. How do I set these configuration registers so I can get an optimal phase noise and fractional spur performance?