Tool/software:

Dear Experts,

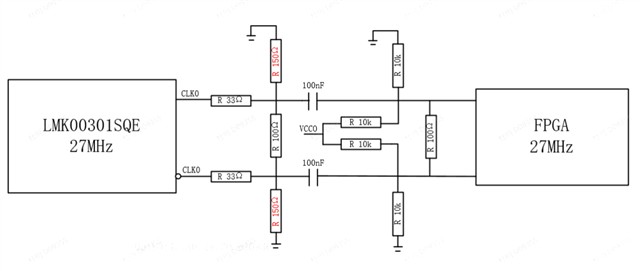

The design schematic diagram is as follows.The design schematic diagram is as follows. Our current FPGA design requirements are: differential input voltage range of 100mV~600mV, common mode input voltage range of 300mV~1125mV, and single ended input voltage overshoot range of -200mV-1200mV. We would like to inquire about the design of clock impedance matching circuit and hope to receive answers. Thank you~

1. Do we need a 150 Ω resistor to ground the AC coupling capacitor?

2. When laying out a single PCB, is it necessary to place the matching circuits of the sending and receiving ends close to the ports respectively? Should AC coupling capacitors also be placed near the transmitting end?